330

CHAPTER 14 8-BIT SERIAL I/O

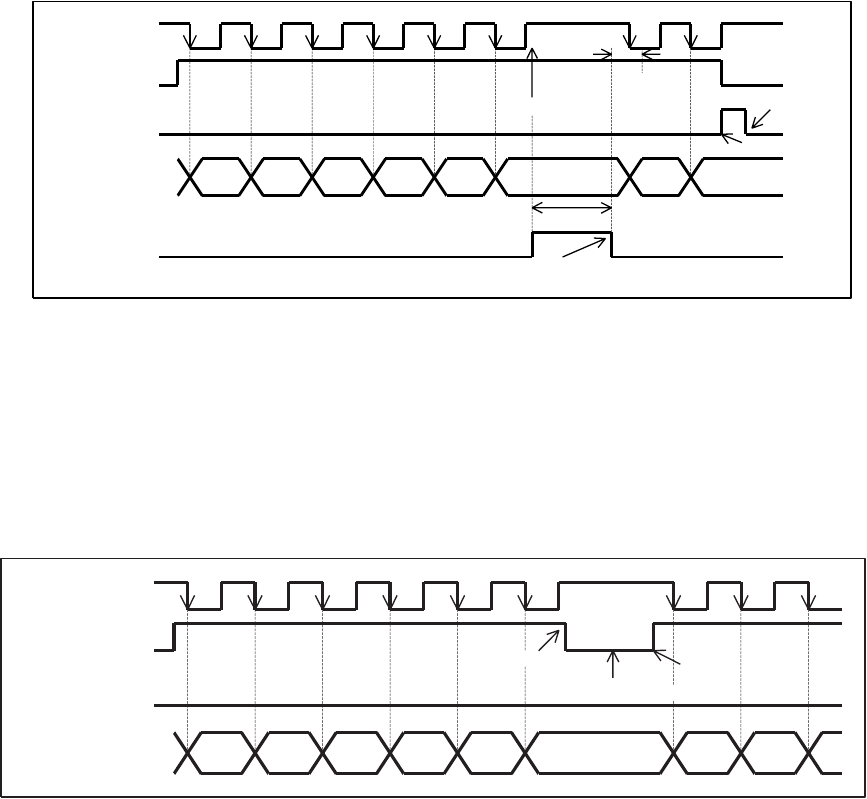

Figure 14.8-2 8-bit Serial I/O Operation in Stop Mode (Internal Shift Clock)

● 8-bit serial I/O operation at issuance of stop request during operation

As shown in Figure 14.8-3 , if operation is stopped (SMR: SST = 0) during data transfer, the 8-bit serial I/O

stops data transfer and clears the shift clock counter. For this reason, the transfer destination must also be

initialized. If serial output is in operation, set the SDR again before restarting the 8-bit serial I/O.

Figure 14.8-3 8-bit Serial I/O Operation at Issuance of Stop Request during Operation(Internal Shift Clock)

#0 #1 #2 #4#3 #5 #6 #7

SCK output

SST bit

Oscillation stabilization

wait time

Stop mode request

Clear via program

SIOF bit

Interrupt request

SO pin output

STP bit

(STBC register)

Stop mode

Stop mode release via external interrupt

#0 #1 #2 #4#3 #5 #0 #1

SCK output

SST bit

Operation stop

Restart

SDR register resetting

SIOF bit

SO pin output