303

CHAPTER 13 UART

13.5 Interrupt of UART

UART supports the interrupt-related error flag bit (ORFE), received data flag bit (RDRF),

and transmitted data flag bit (TDRE), and the following interrupt sources:

• When received data is sent from the reception shift register to the serial input data

register (SIDR). (Reception interrupt)

• When transmitted data is sent from the serial output data register (SODR) to the

transmission shift register. (Transmission interrupt)

■ Transmission Interrupt

When the SSD register is read and the output data is written into the SODR register, the data written into

the SODR register is transferred to the internal transmission shift register. When next data becomes

writable, the TDRE bit is set to "1", then an interrupt request to the CPU (IRQ5) is generated if the

transmission interrupt is enabled (SSD: TIE = 1).

■

Reception Interrupt

● When operating mode is 0, 1, or 3

When data is correctly input up to the stop bit, the RDRF bit is set to "1". If an overrun error or framing

error occurs, the ORFE bit is set to "1".

These bits are set when a stop bit is detected. If the reception interrupt is enabled (SSD: RIE = 1), an

interrupt request to the CPU (IRQ6) is generated.

● When operating mode is 2

For both RDRF and ORFE, data is received or transmitted with the final data bit (D8) set to "1", these flags

go on when the stop bit at the end is detected. However, when the framing error occurs, the flag goes on

regardless of the final data bit. An interrupt request to the CPU is generated when the flag goes on and the

input data becomes "1".

■

UART Interrupt Related Registers and Vector Table Addresses

Table 13.5-1 provides the registers relating to the UART interrupts and vector table addresses. For details

of the interrupt operation, see Section "3.4.2 Steps in the Interrupt Operation ".

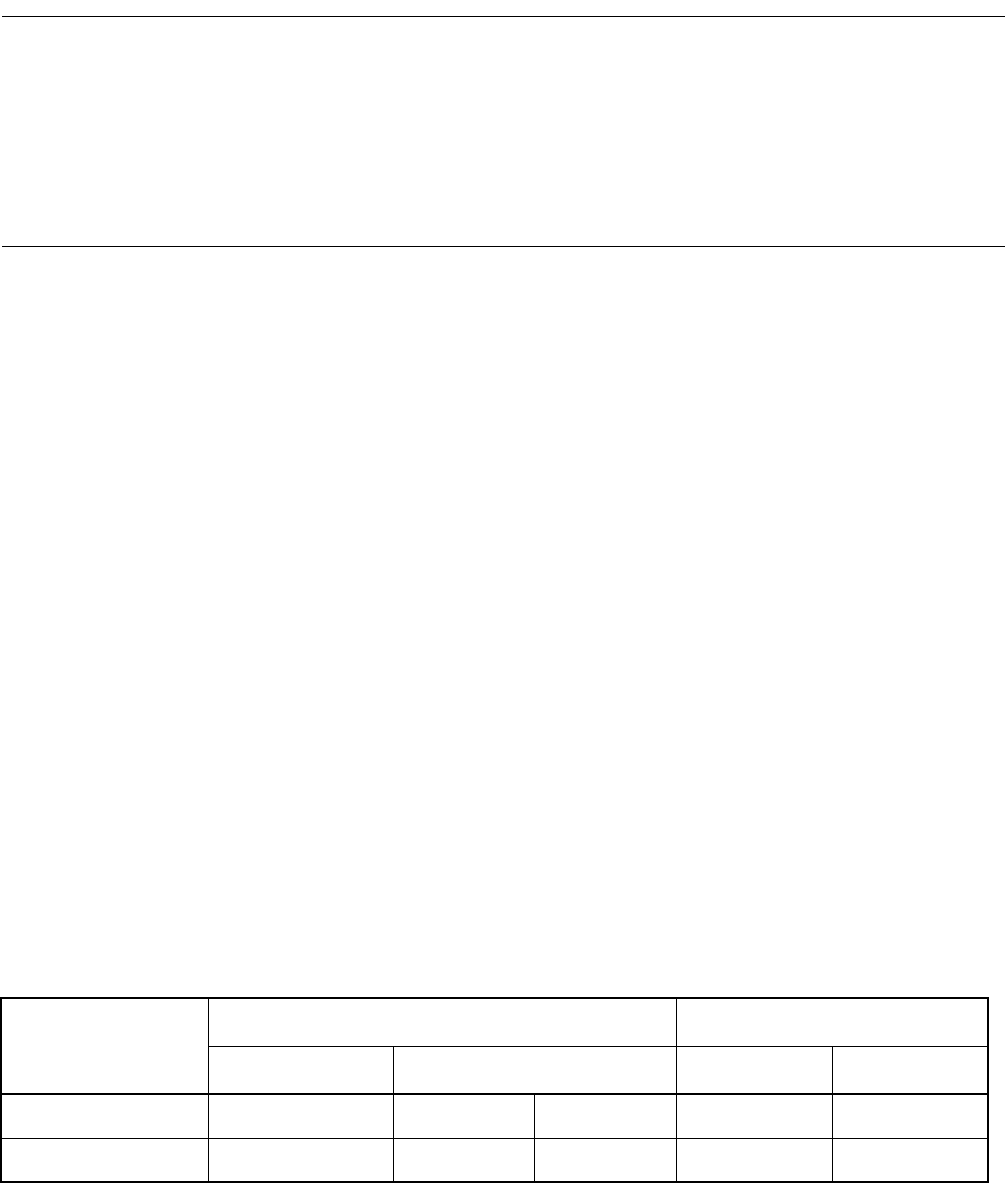

Table 13.5-1 UART Interrupt Related Registers and Vector Table Addresses

Interrupt name

Interrupt level setting register Vector table address

Register Bit Upper digits Lower digits

IRQ5

ILR2 (007C

H

)

L51 (bit3) L50 (bit2)

FFF0

H

FFF1

H

IRQ6

ILR2 (007C

H

)

L61 (bit5) L60 (bit4)

FFEE

H

FFEF

H