57

CHAPTER 3 CPU

■

Instruction Cycle (t

INST

)

For instruction cycles (minimum instruction run time), a 1/4, 1/8, 1/16, or 1/64 frequency can be selected

using the clock speed selection bits (CS1 and CS0).

In active mode, when the oscillation frequency (F

CH

) is 12.5 MHz, the instruction cycle for the maximum

speed (SYCC: CS1 and CS0 = 11

B

) is 4/F

CH

(= about 0.32 µs).

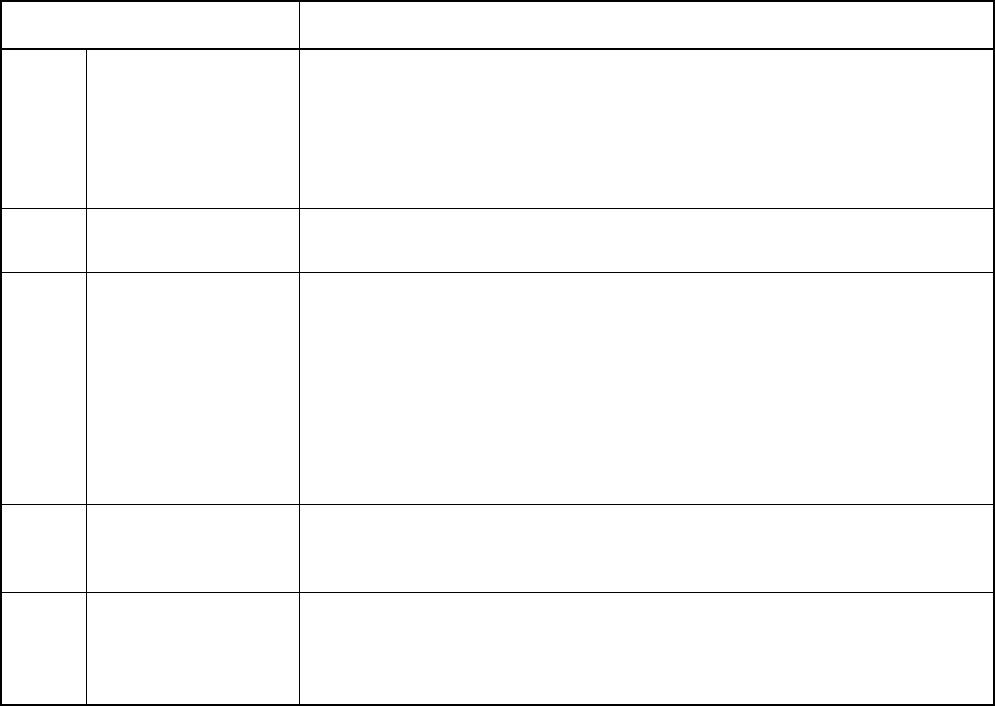

Table 3.6-1 Explanation of Functions of Each Bit in the System Clock Control Register (SYCC)

Bit name Description

bit7

SCM: System clock

monitor bit

Used to check the current clock mode.

When this bit is 0, the clock is stopping or waiting for stabilization of oscillation.

When this bit is 1, operations are performed in active mode.

Note:

This bit is read-only enabled. Writing a value to this bit does not affect

operation.

bit6,

bit5

Unused bits

Values in these bits are undefined when read.

Writing values into these bits does not affect operation.

bit4,

bit3

WT1, WT0:

Oscillation

stabilization wait time

selection bits

Used to select an oscillation stabilization wait time setting.

When external interrupt causes a return from stop mode to active mode, the

oscillation stabilization wait time setting selected by these bits is applied.

The initial values of these bits are determined by options. Therefore, when an

oscillation stabilization wait time setting is to be applied for a reset, it is selected by

options.

Note:

Change values in these bits after confirming that the clock is not waiting for

stabilization of oscillation using the SCM bit.

bit2 Unused bit

This bit is always "1" when read.

Note:

Specify "1".

bit1,

bit0

CS1, CS0:

Clock speed selection

bits

Used to select the clock speed in active mode.

One of four operating clock speeds (gears) can be specified for the CPU and

peripheral functions. However, these bits do not affect the operating clock for the

time-base timer.