CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 91

FR81 Family

CHAPTER 6 INSTRUCTION OVERVIEW

6.2

TYPE-N

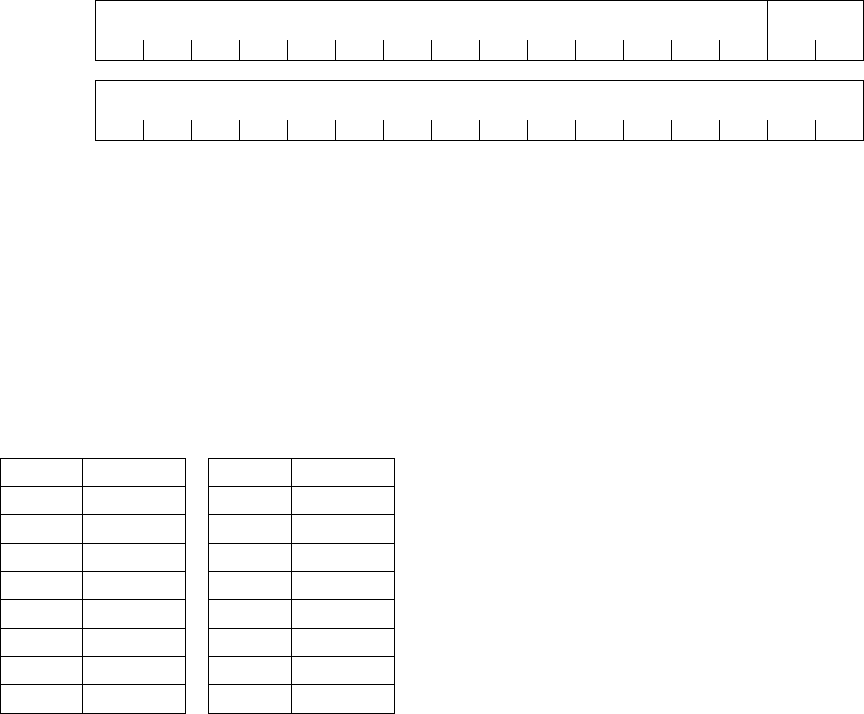

It has 14-bit OP Code (OP) and floating point register list (frlist). These are the instruction formats

that have been added to FR81 Family CPU.

6.2.4 Register designated Field

● General-purpose register designated Field (Ri/Rj)

Among Instruction formats, fields that designate general-purpose register are 4-bit length Ri and Rj.

Relation between bit pattern of general purpose register and register designated field has been indicated in

Table 6.2-1.

Table 6.2-1 Bit pattern of general purpose register and register designated field

MSB LSB

(n+0) OP -

(n+2) frlist

Ri / Rj Register Ri / Rj Register

0000

B

R0

1000

B

R8

0001

B

R1

1001

B

R9

0010

B

R2

1010

B

R10

0011

B

R3

1011

B

R11

0100

B

R4

1100

B

R12

0101

B

R5

1101

B

R13

0110

B

R6

1110

B

R14

0111

B

R7

1111

B

R15