FR81 Family

144 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.20

● Flag Change

N, Z, V, C: Unchanged.

● Classification

Delayed branching instruction

● Execution Cycles

1 cycle

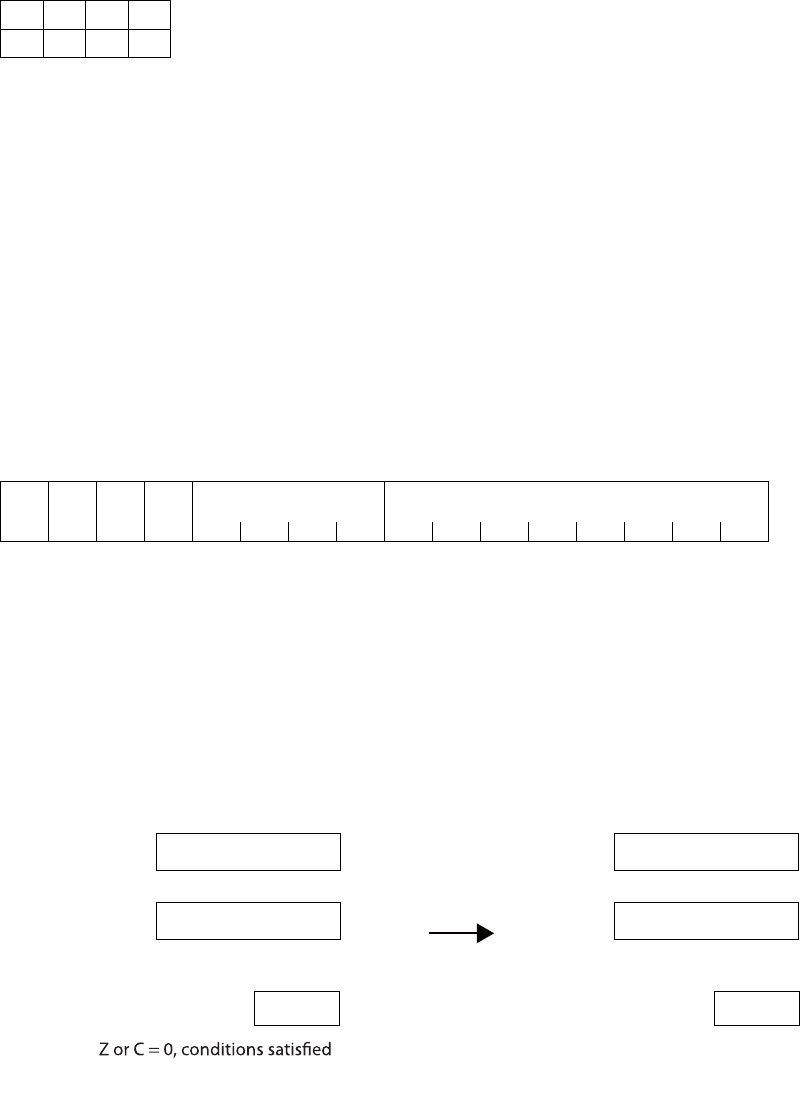

● Instruction Format

● Execution Example

BHI:D label ; Bit pattern of the instruction: 1111 1111 0010 1000

LDI:8 #255, R1 ; Instruction placed in delay slot

. . .

label: ; BHI:D instruction address + 50H

The instruction placed in delay slot will be executed before the execution of the branch destination

instruction. The value of R1 above will vary according to the specifications of the LDI:8 instruction placed

in the delay slot.

NZVC

----

MSB LSB

1111 cc rel8

PC PC

FF8 0 0052FF8 0 0000

R1 R1

0000 00FF8 947 97AF

NZVC

CCR CCR

NZVC

10101010

Before execution After execution