FR81 Family

CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 37

CHAPTER 3 PROGRAMMING MODEL

3.3

3.3.15 Exception status register (ESR)

This is a 32-bit register that indicates the balance of process when an exception occurs while executing the

invalid instruction exception source and the multiple load/store instruction.

The exception status register (ESR) consists of the following two parts:

• Register list (RL)

• Invalid instruction exception source (INV)

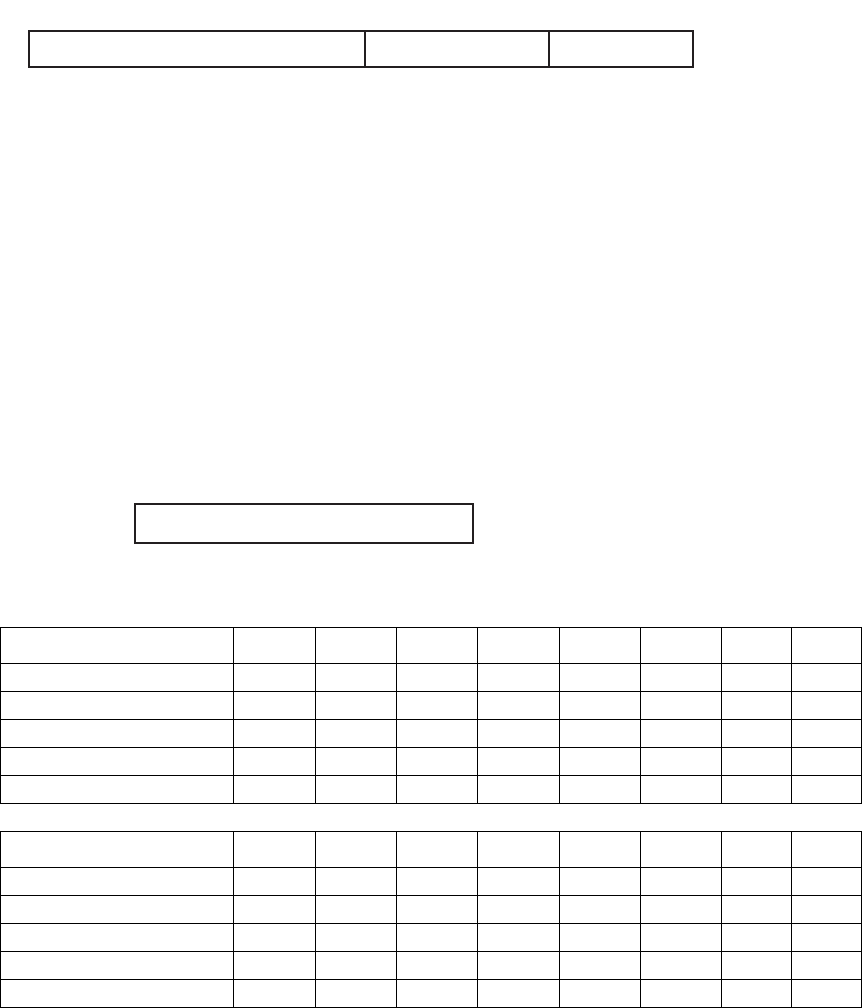

Figure 3.3-28 shows the bit configuration of the exception status register (ESR).

Figure 3.3-28 Exception status register (ESR) Bit Configuration

The reserved bits of the exception status register (ESR) are all reserved for future expansion. The read

value of reserved bits is always "0". Write value should always be "0".

■ Register List (RL)

Register list (RL) is a 16-bit register that indicates registers whose transmission has not ended when an

exception occurs while a LDM0, LDM1, STM0, STM1, FLDM, or FSTM instruction is executed. It lies

between bit 31 and bit 16 of the exception status register (ESR). The register list (RL) value is updated only

when an exception occurs while a LDM0, LDM1, STM0, STM1, FLDM, or FSTM instruction is executed.

Figure 3.3-29 shows the bit configuration of the register list (RL), and Table 3.3-11 shows the

correspondence between the register list (RL) bits and the registers.

Figure 3.3-29 Register List (RL) Bit Configuration

bit31 bit16 bit15 bit7 bit6

bit0

RL Reserved INV

bit31 bit16

RL15 RL0

Initial value

0000

H

Table 3.3-11 Correspondence between the register list (RL) bits and the registers

bit of ESR register 31 30 29 28 27 26 25 24

RL bit RL15RL14RL13RL12RL11RL10RL9RL8

LDM1, LDM0 instruction R15 R14 R13 R12 R11 R10 R9 R8

STM1, STM0 instructionR0R1R2R3R4R5R6R7

FLDM instruction FR15 FR14 FR13 FR12 FR11 FR10 FR9 FR8

FSTM instruction FR0 FR1 FR2 FR3 FR4 FR5 FR6 FR7

ESR bit 2322212019181716

RL bit RL7 RL6 RL5 RL4 RL3 RL2 RL1 RL0

LDM1, LDM0 instructionR7R6R5R4R3R2R1R0

STM1, STM0 instruction R8 R9 R10 R11 R12 R13 R14 R15

FLDM instruction FR7 FR6 FR5 FR4 FR3 FR2 FR1 FR0

FSTM instruction FR8 FR9 FR10 FR11 FR12 FR13 FR14 FR15