FR81 Family

436 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

APPENDIX

APPENDIX A Instruction Lists

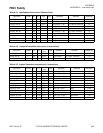

Table A.2-4 Bit Operation Instructions (8 Instructions)

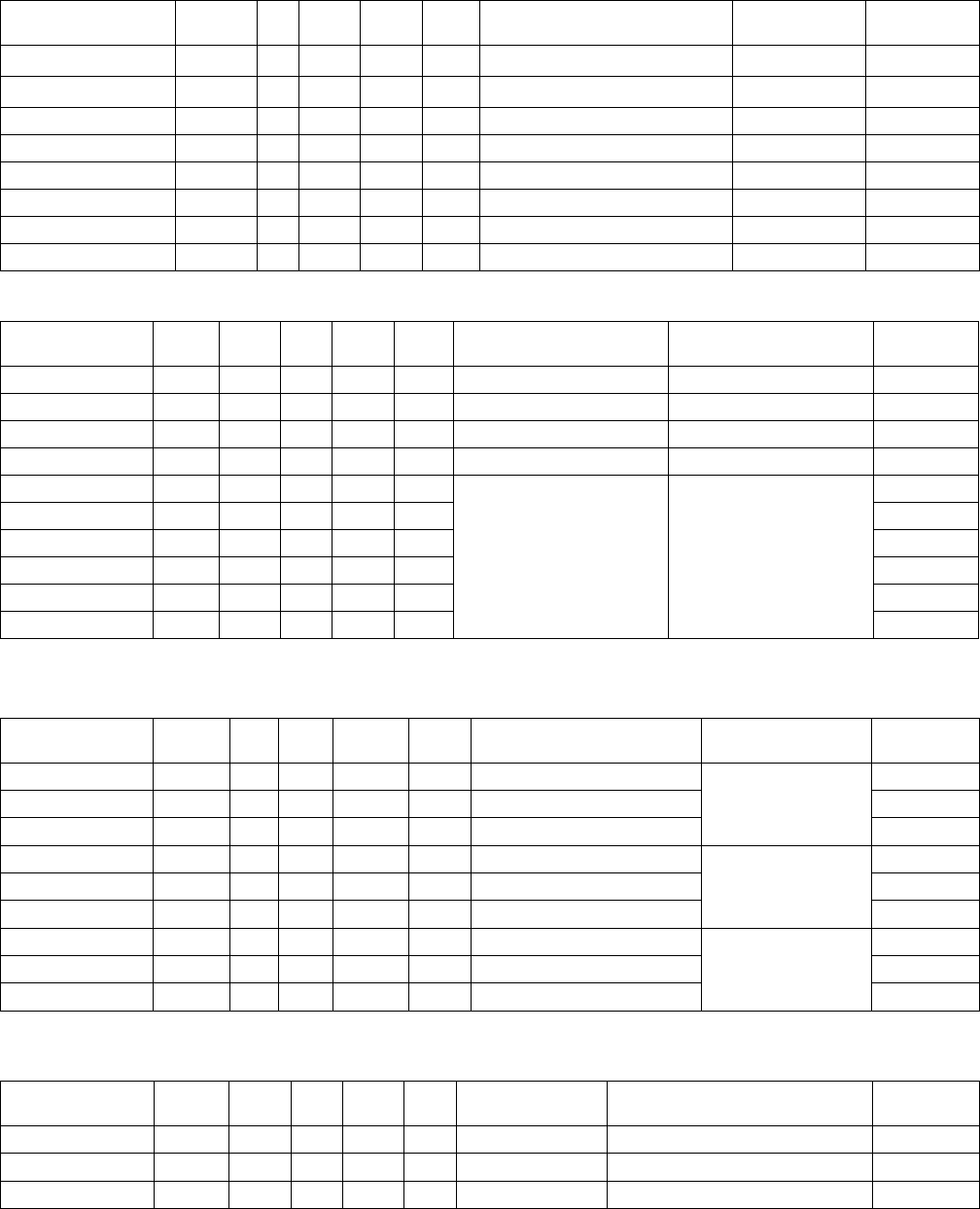

Table A.2-5 Multiply/ Divide Instructions (10 Instructions)

Table A.2-6 Shift Instructions (9 Instructions)

Table A.2-7 Immediate Data Transfer Instructions (3 Instructions)

Mnemonic Format

OP CYC

FLAG

NZVC

RMW

Operation Remarks Reference

BANDL #u4, @Ri C 80 1+2a ---- ❍

(Ri) & {F0

H

+u4} → (Ri)

Lower 4- bit 7.18

BANDH #u4, @Ri C 81 1+2a ---- ❍

(Ri) & {u4<<4+0F

H

} → (Ri)

Higher 4 bit 7.17

BORL #u4, @Ri C 90 1+2a ---- ❍ (Ri) | u4 → (Ri) Lower 4- bit 7.24

BORH #u4, @Ri C 91 1+2a ---- ❍ (Ri) | {u4<<4} → (Ri) Higher 4 bit 7.23

BEORL #u4, @Ri C 98 1+2a ---- ❍ (Ri) ^ u4 → (Ri) Lower 4- bit 7.22

BEORH #u4, @Ri C 99 1+2a ---- ❍ (Ri) ^ {u4<<4} → (Ri) Higher 4 bit 7.21

BTSTL #u4, @Ri C 88 2+a 0C-- - (Ri) & u4 Lower 4- bit 7.26

BTSTH #u4, @Ri C 89 2+a CC-- - (Ri) & {u4<<4} Higher 4 bit 7.25

Mnemonic

Format OP CYC

FLAG

NZVC

RMW

Operation Remarks

Reference

MUL Rj, Ri A AF 5

CCC-

-Ri × Rj → MDH,MDL 32 × 32 bit = 64 bit 7.133

MULU Rj, Ri A AB 5

CCC-

-Ri × Rj → MDH,MDL Unsigned 7.135

MULH Rj, Ri A BF 3

CC--

-Ri × Rj → MDL 16 × 16 bit = 32 bit 7.134

MULUH Rj, Ri A BB 3

CC--

-Ri × Rj → MDL Unsigned 7.136

DIV0S Ri E 97-4 1

----

-

In the Specified

Instruction Sequence

MDL ÷ Ri → MDL

MDL%Ri → MDH

Step Calculation

32 ÷ 32 bit = 32 bit

7.34

DIV0U Ri E 97-5 1

----

-7.35

DIV1 Ri E 97-6 1

-C-C

-7.36

DIV2 Ri E 97-7 c

-C-C

-7.37

DIV3 E’ 9F-6 1

----

-7.38

DIV4S E’ 9F-7 1

----

-7.39

Mnemonic

Format

OP CYC

FLAG

NZVC

RMW

Operation Remarks

Reference

LSL Rj, Ri A B6 1 CC-C - Ri << Rj → Ri

Logical Shift

7.120

LSL #u4, Ri C B4 1 CC-C - Ri << u4 → Ri 7.121

LSL2 #u4, Ri C B5 1 CC-C - Ri << {u4+16} → Ri 7.122

LSR Rj, Ri A B2 1 CC-C - Ri >> Rj → Ri

Logical Shift

7.123

LSR #u4, Ri C B0 1 CC-C - Ri >> u4 → Ri 7.124

LSR2 #u4, Ri C B1 1 CC-C - Ri >> {u4+16} → Ri 7.125

ASR Rj, Ri A BA 1 CC-C - Ri >> Rj → Ri

Arithmetic Shift

7.14

ASR #u4, Ri C B8 1 CC-C - Ri >> u4 → Ri 7.15

ASR2 #u4, Ri C B9 1 CC-C - Ri >> {u4+16} → Ri 7.16

Mnemonic

Format

OP CYC

FLAG

NZVC

RMW

Operation Remarks

Reference

LDI:32 #i32, Ri H 9F-8 d ---- - i32 → Ri 7.107

LDI:20 #i20, Ri G 9B d ---- - extu(i20) → Ri

Higher 12-Bits are Zero extension

7.106

LDI:8 #i8, Ri B C0 1 ---- - extu(i8) → Ri

Higher 24-Bits are Zero extension

7.108