FR81 Family

302 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.109

7.109 LDM0 (Load Multiple Registers)

The LDM0 instruction stores the word data from the address R15 to the registers in the

range R0 to R7 as members of the parameter reglist and repeats the operation of adding

4 to R15. Registers are processed in ascending numerical order.

● Assembler Format

LDM0 (reglist)

Registers from R0 to R7 are separated in reglist, multiple register are arranged and specified.

● Operation

The following operations are repeated according to the number of registers specified in the parameter

reglist.

(R15) → Ri

R15+4 → R15

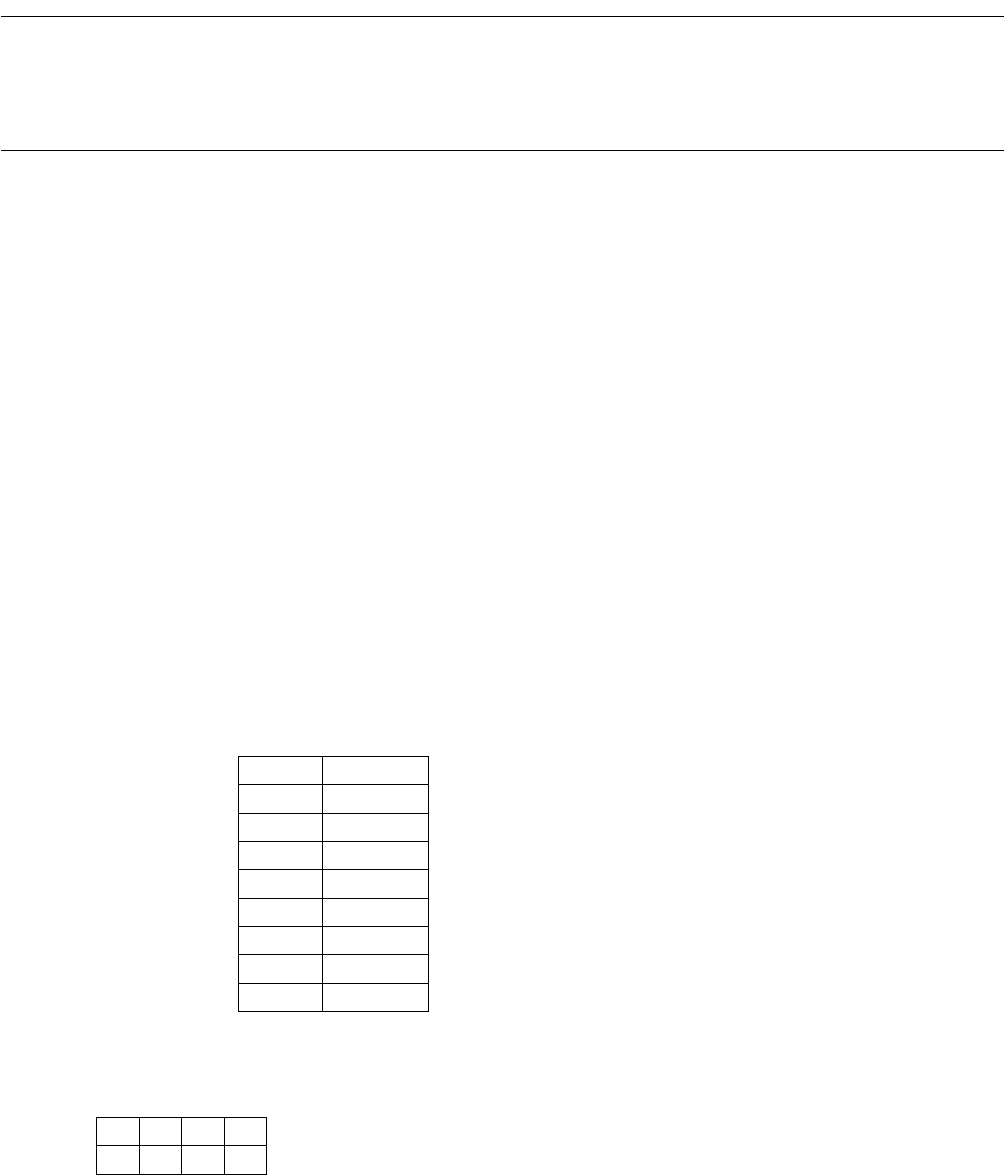

Bit values and register numbers for reglist (LDM0) are shown in Table 7.109-1.

Table 7.109-1 Bit values and register numbers for reglist (LDM0)

● Flag Change

N, Z, V, C: Unchanged.

Bit Register

7R7

6R6

5R5

4R4

3R3

2R2

1R1

0R0

NZVC

----