CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 73

FR81 Family

CHAPTER 5 PIPELINE OPERATION

5.2

5.2 Pipeline Operation and Interrupt Processing

It is possible at times that an event wherein it appears that interrupt request is lost after

acceptance of interrupt, if the flag that causes interrupt in the interrupt-enabled

condition, because pipeline operation is conducted, occurs.

5.2.1 Mismatch in Acceptance and Cancellation of Interrupt

Because CPU is carrying out pipeline processing, pipeline processing of multiple instructions is already

executed at the time of acceptance of interrupt. Therefore, in case corresponding interrupt cancellation

processing among the instructions under execution in the pipeline (For example, clearing of flag bits that

cause interrupt) is carried out, branching to corresponding interrupt processing program is carried out

normally but when control is transferred to interrupt processing, the interrupt request is at times already

over (Flag bits that cause interrupt having been cleared).

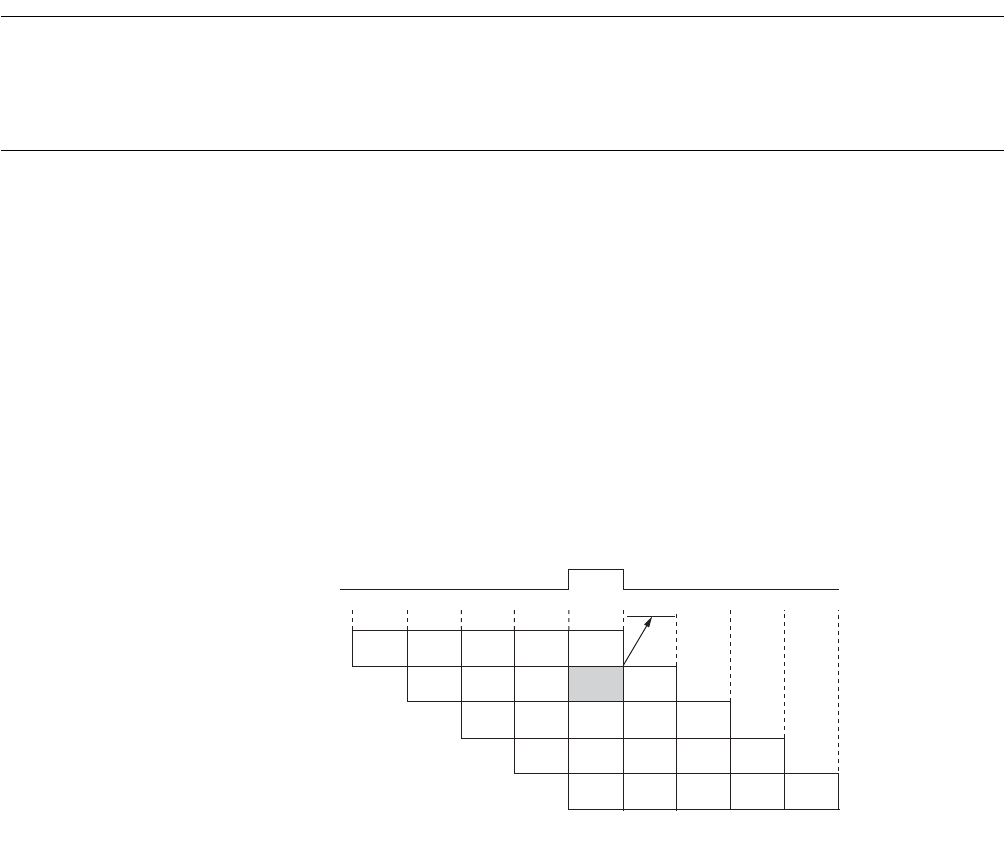

An Example of Mismatch in Acceptance and cancellation of interrupt is shown is Figure 5.2-1.

Figure 5.2-1 Example of Mismatch in Acceptance and Cancellation of interrupt

This type of phenomenon does not occur in case of exceptions and trap, because the operation for request

cancellation cannot be carried out in the program.

5.2.2 Method of preventing the mismatched pipeline conditions

Mismatch in Acceptance and Deletion of interrupt can occur in case flag bits that cause interrupt are

cleared while interrupt request is enabled in the peripheral functions.

To avoid such a phenomenon, programmers should set the interrupt enable flag (I) at "0", disable interrupt

acceptance in CPU and clear the flag bits that cause an interrupt.

IF ID EX MA WB

IF ID EX MA WB

IF ID --

--: Canceled stages

-- --

-- -- -- --

IF

IF ID EX MA WB

LD @R10, R1

Interrupt request

ADD R1, R3(cancelled)

BNE Te stOK(cancelled)

EIT sequence execution #1

ST R2, @R11

None None None None None None None

Generated Canceled