CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 63

FR81 Family

CHAPTER 4 RESET AND "EIT" PROCESSING

4.8

4.8 Timing When Register Settings Are Reflected

The timing when the new values are reflected after the interrupt enable flag (I) of

program status (PS) and the value of interrupt level mask register (ILM) are modified will

be explained in this section.

4.8.1 Timing when the interrupt enable flag (I) is requested

The interrupt request (enable/disable) is reflected from the instruction which modifies the value of interrupt

enable flag (I).

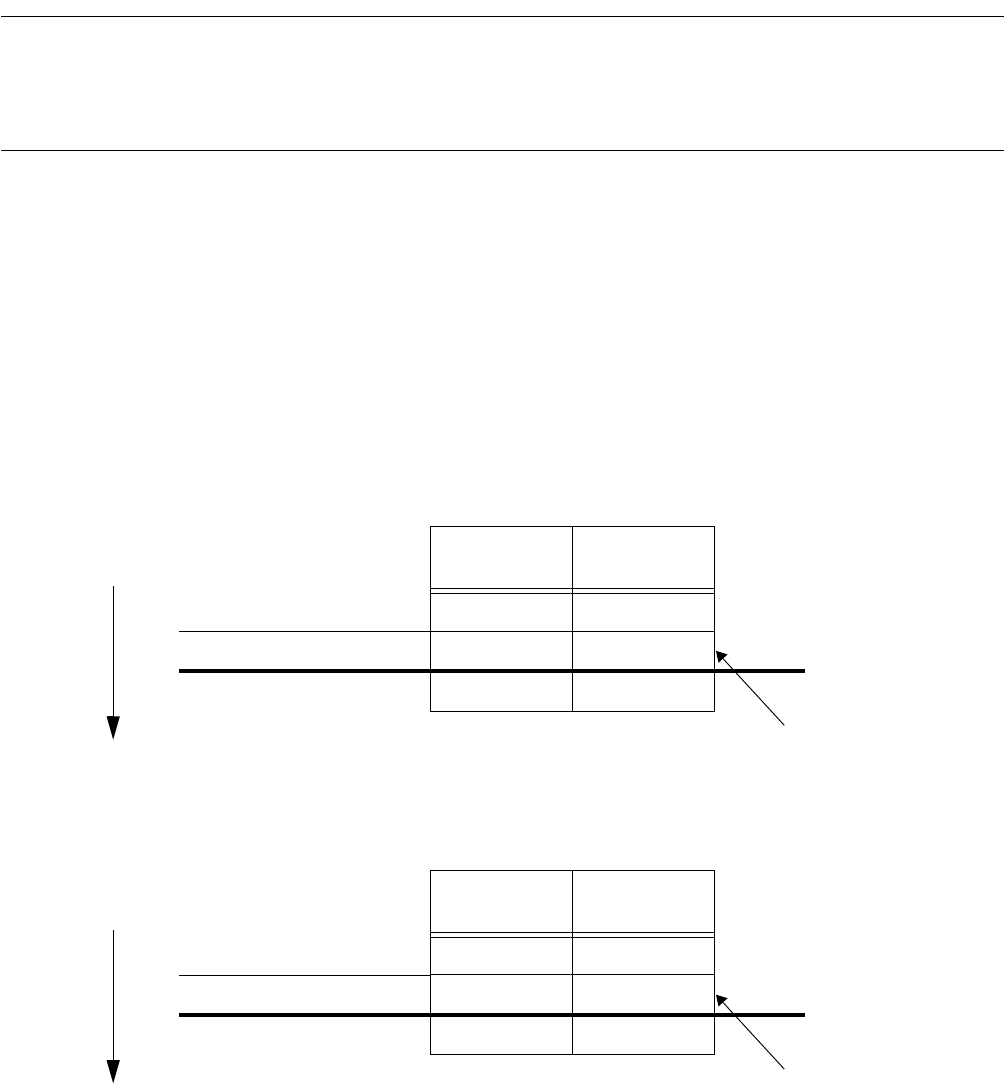

Figure 4.8-1 shows the timing of reflection of the interrupt enable flag (I) when interrupt enable is set to

(I=1), and Figure 4.8-2 shows the timing of reflection of the interrupt enable flag (I) when interrupt disable

is set to (I=0).

Figure 4.8-1

Timing of reflection of interrupt enable flag (I) when interrupt enable is set to (I=1)

Figure 4.8-2 Timing of reflection of interrupt enable flag (I) when interrupt disable is set to (I=0)

Instruction

execution

I flag Interrupt

Instruction 0 Disable

ORCCR #10H 1 Enable

Instruction 1 Enable

Interrupt enabled from here

Instruction

execution

I flag Interrupt

Instruction 1 Enable

ANDCCR #EFH 0 Enable

Instruction 0 Disable

Interrupt disabled from here