CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 253

FR81 Family

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.79

7.79 FMSUBs (Single Precision Floating Point Multiply and

Subtract)

FRk is multiplied by FRj, and its result is subtracted by FRi and then stored in FRi.

● Assembler Format

FMSUBs FRk, FRj, FRi

● Operation

FRk × FRj - FRi → FRi

● Classification

Single-precision floating point instruction, FR81 family

● Execution Cycles

4 cycles

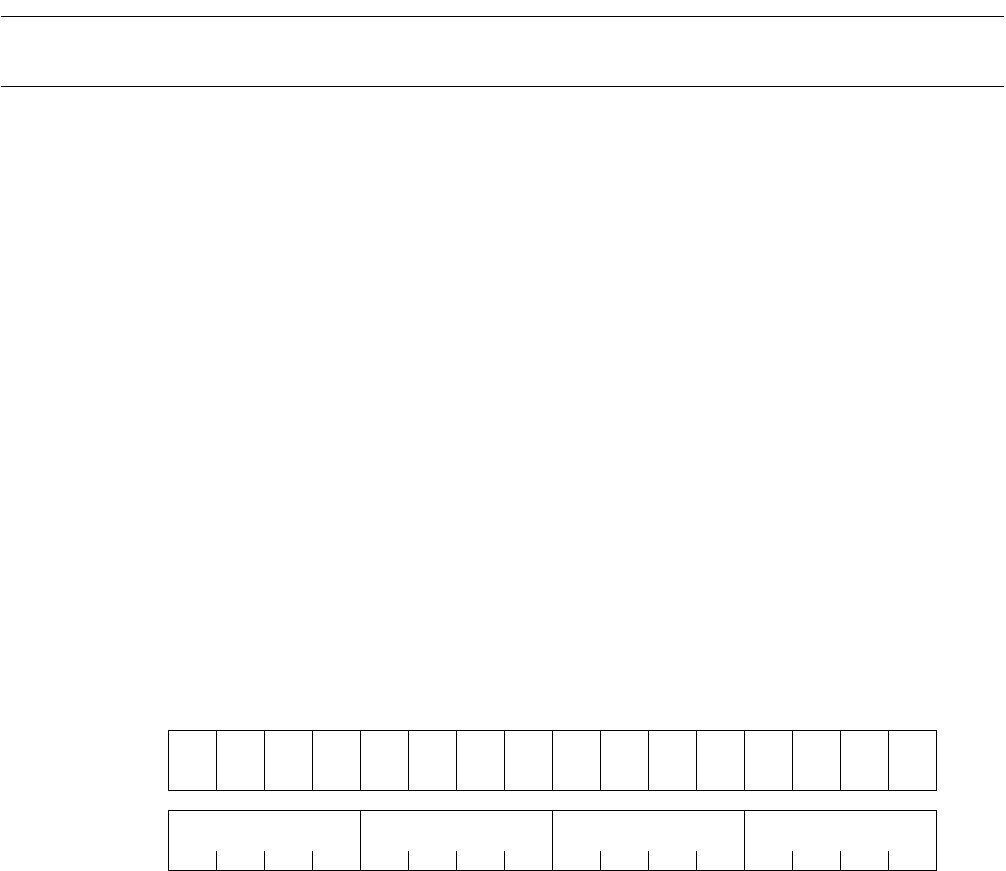

● Instruction Format

● EIT Occurrence and Detection

An invalid instruction exception (FPU absence error), an FPU exception, or an interrupt is detected.

MSB LSB

(n+0)0000011110100110

(n+2) - FRk FRj FRi