FR81 Family

358 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.139

7.139 OR (Or Word Data of Source Register to Destination

Register)

Takes the logical OR of the word data in Ri and the word data in Rj, stores the results to

Ri.

● Assembler Format

OR Rj, Ri

● Operation

Ri | Rj → Ri

● Flag Change

N: Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z: Set when the operation result is zero, cleared otherwise.

V, C: Unchanged.

● Classification

Logical Calculation instruction, Instruction with delay slot

● Execution Cycles

1 cycle

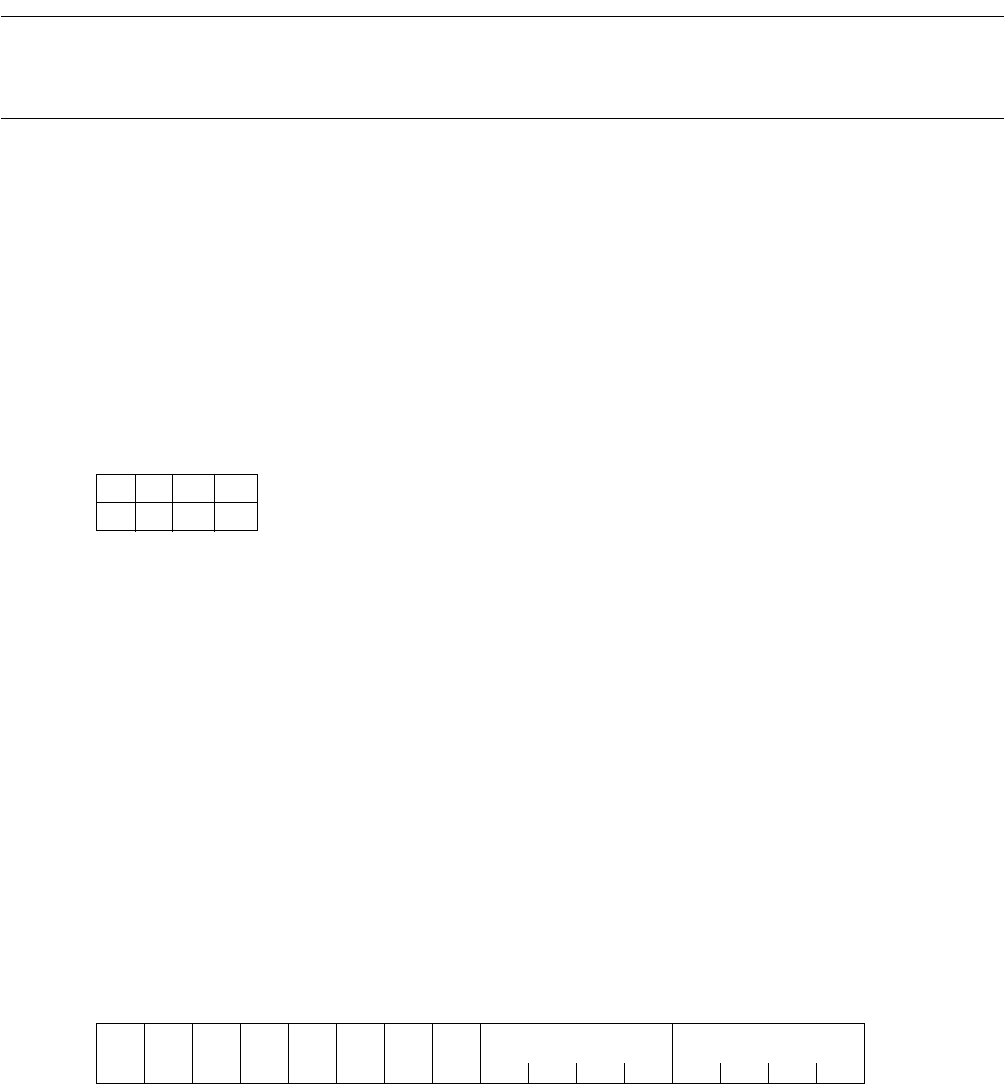

● Instruction Format

NZV C

CC - -

MSB LSB

10010010 Rj Ri