FR81 Family

280 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.97

7.97 LCALL:D (Long Call Subroutine)

This is a branching instruction with a delay slot. The next instruction address is stored

in the return pointer (RP), and then control branches to the address identified by label21

relative to the program counter (PC). The value in rel20 is doubled during address

calculation, and its sign is extended.

● Assembler Format

LCALL:D label21

● Operation

PC + 6 → RP

PC + 4 + exts(rel20 × 2) → PC

● Flag Change

N, Z, V, C: Unchanged.

● Classification

Branching instruction with delay, FR81 family

● Execution Cycles

1 cycle

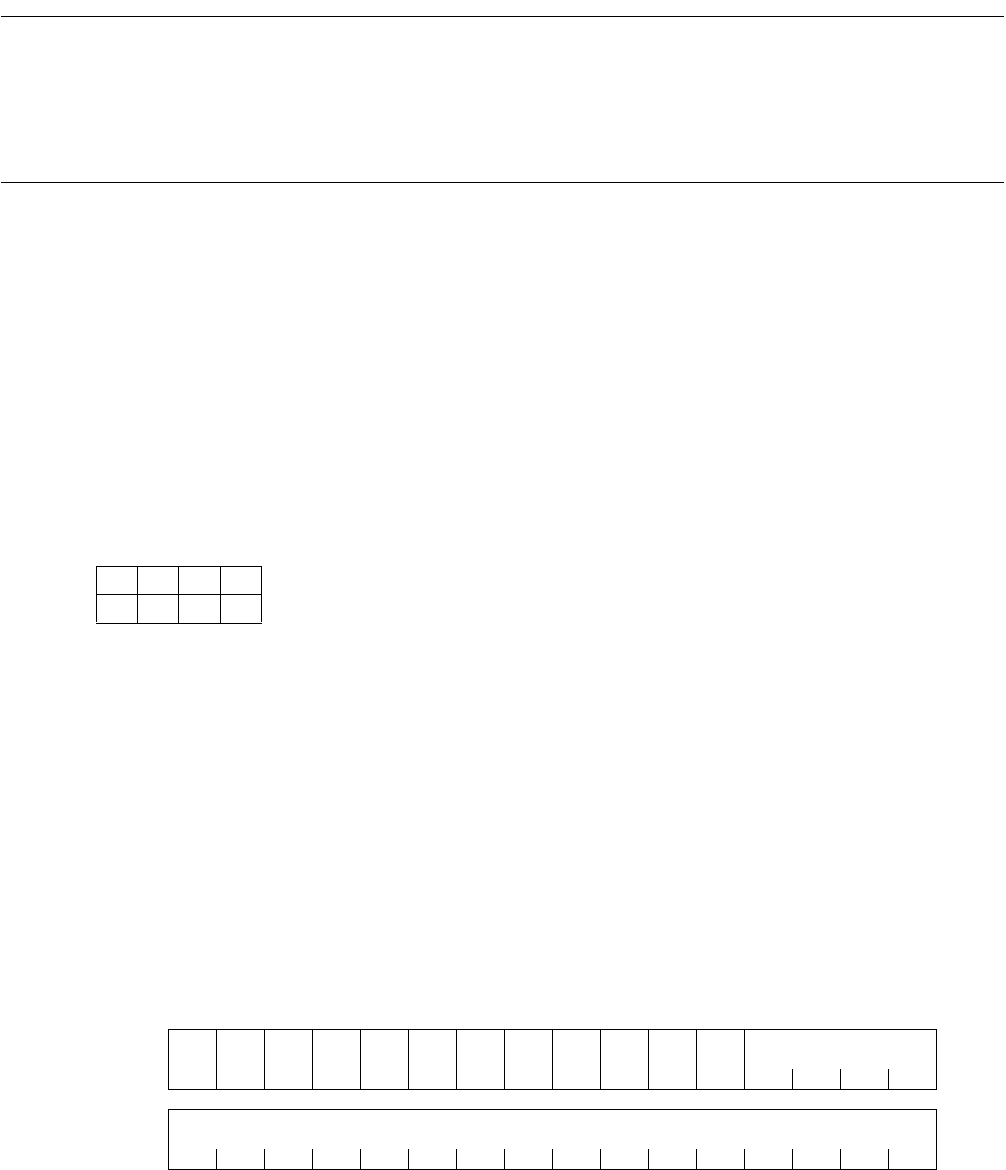

● Instruction Format

● EIT Occurrence and Detection

No interrupt is detected.

NZVC

----

MSB LSB

(n+0)000101110010 rel20 (Upper)

(n+2) rel20 (Lower)