CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 109

FR81 Family

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.3

7.3 ADD2 (Add 4bit Immediate Data to Destination Register)

Adds the result of the higher 28 bits of 4-bit immediate data with minus extension (-16

to -1) to word data in Ri, stores results to Ri. Unlike SUB instruction, changing C flag of

this instruction becomes it as well as the ADD instruction unlike the SUB instruction.

● Assembler Format

ADD2 #i4, Ri

● Operation

Ri + extn(i4) → Ri

● Flag Change

N: Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z: Set when the operation result is zero, cleared otherwise.

V: Set when an overflow has occurred as a result of the operation, cleared otherwise.

C: Set when a carry has occurred as a result of the operation, cleared otherwise.

● Classification

Add/Subtract Instruction, Instruction with delay slot

● Execution Cycles

1 cycle

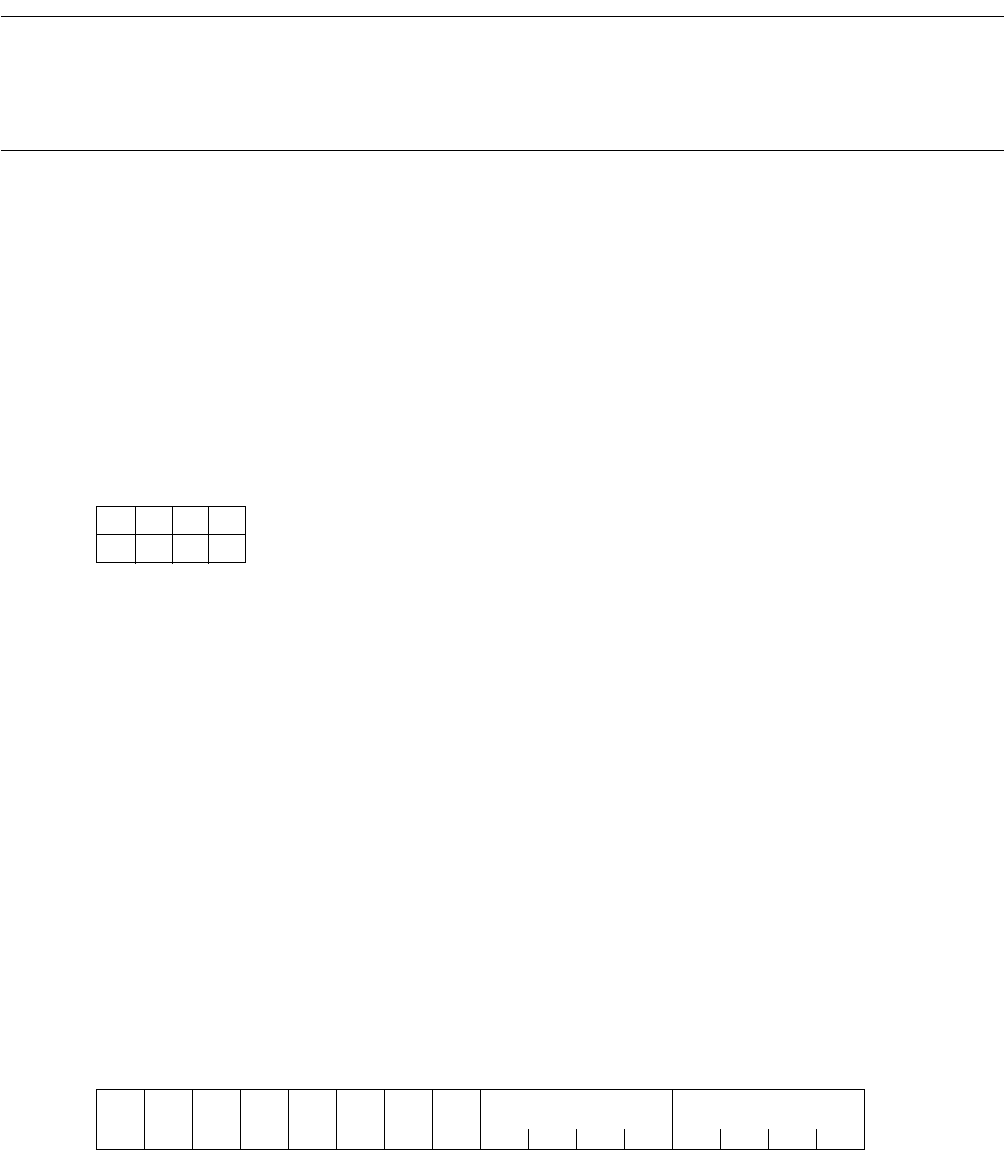

● Instruction Format

NZVC

CCCC

MSB LSB

10100101 i4 Ri