CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 13

FR81 Family

CHAPTER 2 MEMORY ARCHITECTURE

2.2

2.2.4 Byte Order

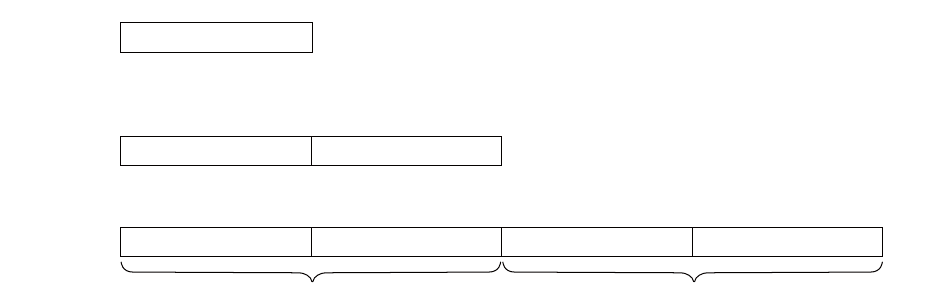

The byte order of FR81 Family CPU is big endian. When word data or half word data are allocated to

address spaces, the higher bytes are placed in the lower address side while the lower bytes are placed in the

higher address side. The arrangement of big endian byte data is shown in Figure 2.2-4.

For example, if a word data was written on the memory (RAM) at address location 0004 1234

H

of the

memory space, the highest byte will be stored at location 0004 1234

H

while the lowest byte will be stored

at location byte 0004 1237

H

.

Figure 2.2-4

Big Endian Byte Orde

MSB

Higher byte Lower byte

LSB

Address Address +1

Half word

MSB

Higher half word Lower half word

LSB

Highest byte Lowest byte

Address Address +1 Address +2 Address +3

Word

MSB

Byte

Address

LSB