FR81 Family

8 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 2 MEMORY ARCHITECTURE

2.1

2.1 Address Space

The address space of FR81 Family CPU is 32 bits (4Gbyte).

CPU controls the address spaces in byte units. An address on the address space is accessed from the CPU

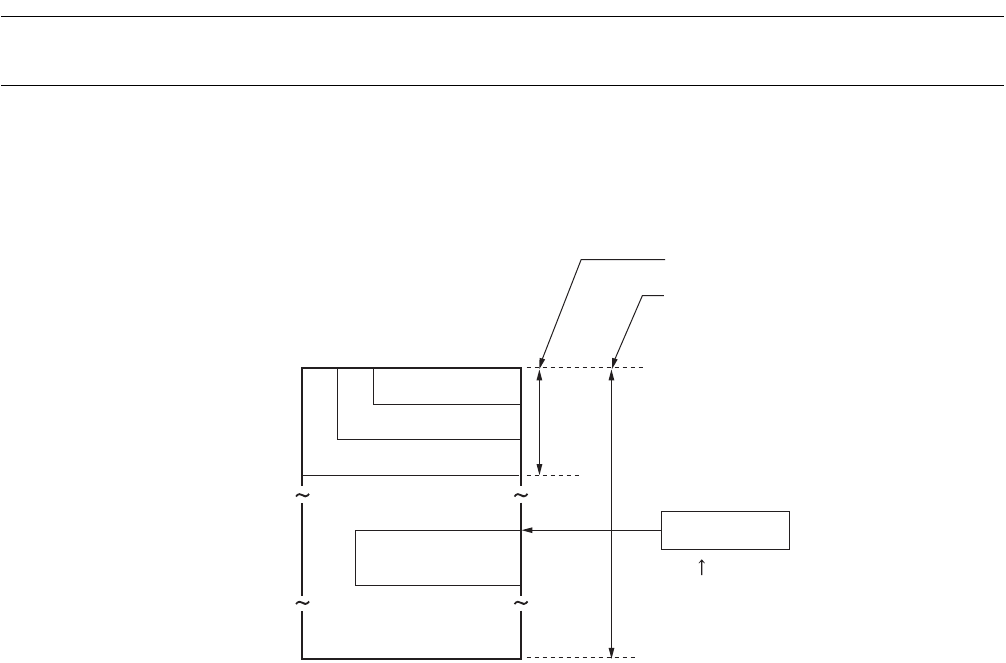

by specifying a 32-bit value. Address space is indicated in Figure 2.1-1.

Figure 2.1-1 Address space

Address space is also called memory space. It is a logical address space as seen from the CPU. Addresses

cannot be changed. Logical address as seen from the CPU, and the physical address actually allocated to

memory or I/O are identical.

2.1.1 Direct Address Area

In the lower address in the address space, there is a direct address area.

Direct address area directly specifies an address in the direct address specification instruction. This area

accesses only based on operand data in the instruction without the use of general-purpose registers. The

size of the address area that can be specified by direct addressing varies according to the data type being

accessed.

The correspondence between data type and area specified by direct address is as follows.

• byte data access: 0000 0000

H

to 0000 00FF

H

• half-word data access: 0000 0000

H

to 0000 01FF

H

• word data access: 0000 0000

H

to 0000 03FF

H

The method of using the 8-bit address data contained in the operand of instructions that specify direct

addresses is as follows:

0000 0000 H

0000 0100 H

0000 0200 H

0000 0400 H

000F FC00H

0010 0000H

FFFF FFFFH

Byte data

Half-word data

Word data

Vector table

initial area

Program or data area

000F FC00

H TBR

TBR initial value

Direct address area

General addressing