FR81 Family

32 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 3 PROGRAMMING MODEL

3.3

3.3.13 Base Pointer (BP)

The base pointer (BP) register is used for pointing in base pointer indirect addressing mode.

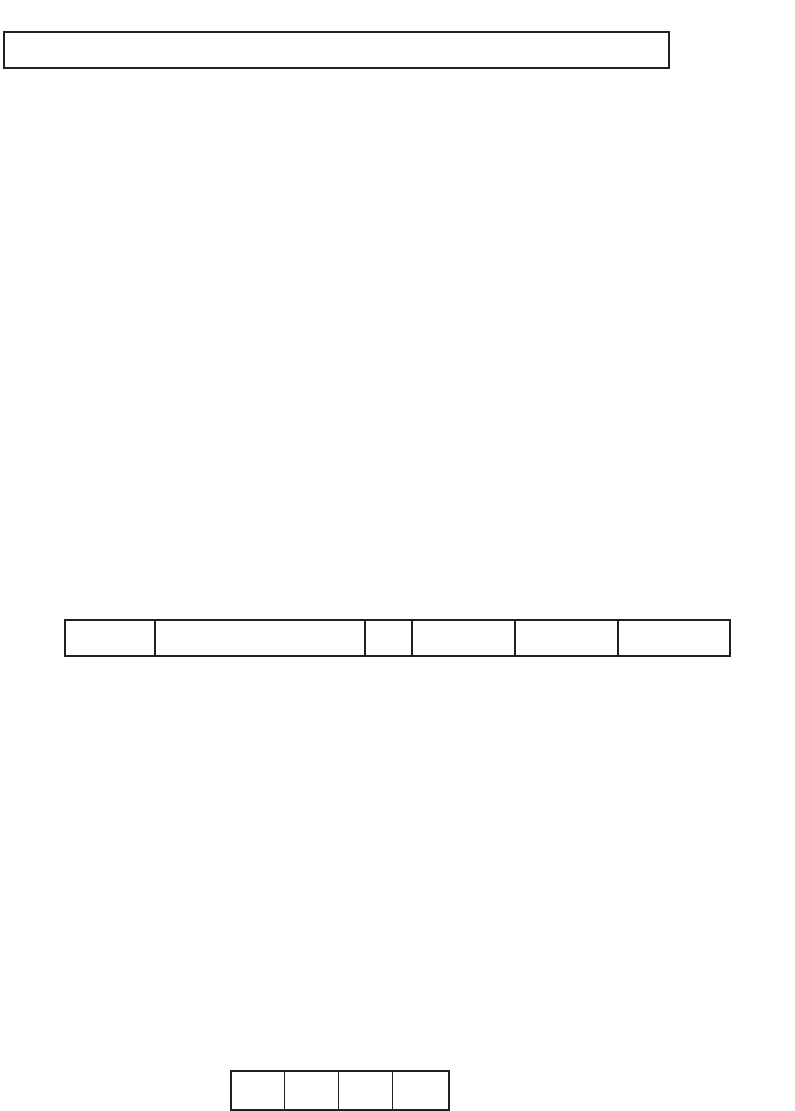

Figure 3.3-21 shows the bit configuration of base pointer (BP).

Figure 3.3-21 Base Pointer (BP) Bit Configuration

3.3.14 FPU Control Register (FCR)

FPU control register (FCR) is a 32-bit register used to control the FPU. It has a flag that indicates the

settings and status of the FPU operation mode.

The FPU control register (FCR) consists of the following five parts:

• Floating point condition code (FCC)

• Rounding mode (RM)

• Floating point exception enable flag (EEF)

• Floating point exception accumulative flag (ECF)

• Floating point exception flag (CEF)

Figure 3.3-22 shows the bit configuration of FPU control register (FCR).

Figure 3.3-22 FPU control register (FCR) Bit Configuration

The reserved bits of the FPU control register (FCR) are all reserved for future expansion. The read value of

reserved bits is always "0". The write value should always be "0".

■ Floating point condition code (FCC)

Floating point condition code (FCC) is a 4-bit register that stores the condition code of a floating point

calculation result. It lies between bit 31 and bit 28 of the FPU control register (FCR).

Figure 3.3-23 shows the bit configuration of the floating point condition code (FCC).

Figure 3.3-23 Floating point condition code (FCC) Bit Configuration

bit31

bit0

Initial value

XXXX XXXX

H

bit31 bit27 bit19 bit17 bit11 bit5

bit0

FCC Reserved RM EEF ECF CEF

bit31 bit30 bit29 bit28

ELGU

Initial value

XXXX

B