CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 71

FR81 Family

CHAPTER 5 PIPELINE OPERATION

5.1

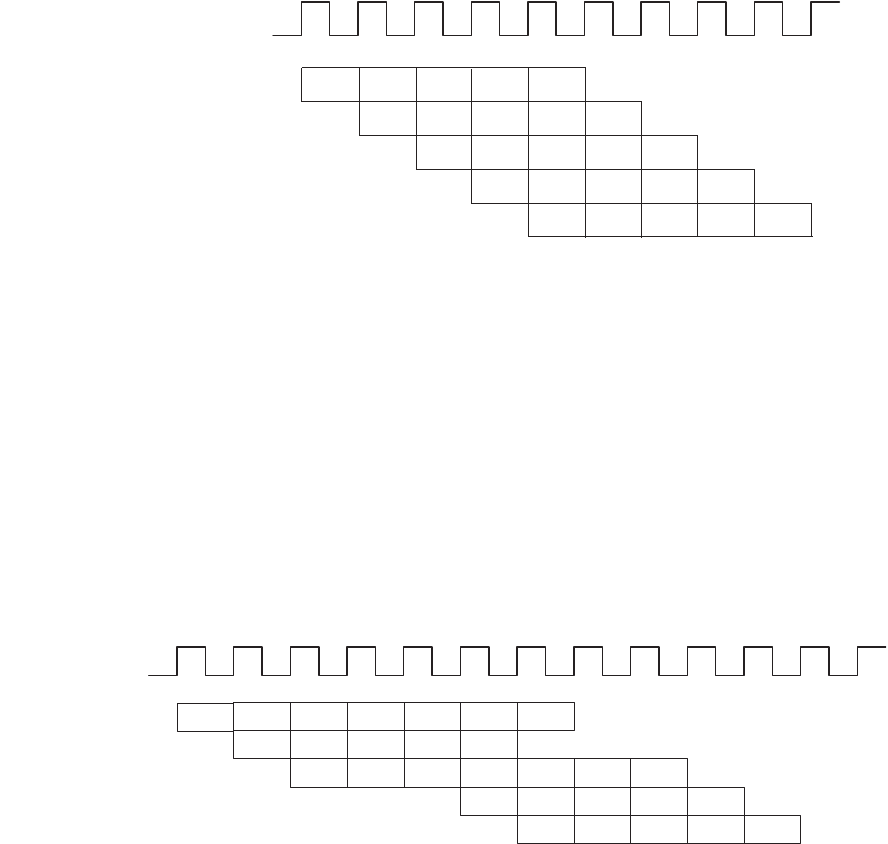

Figure 5.1-1 Example of integer pipeline operation (1)

In principle, execution of instructions is carried out at one instruction per cycle. However, multiple cycles

are necessary for the execution of instruction in case of load store instruction accompanied by memory

wait, non-delayed branching instruction, and multiple cycle instruction. The speed of instruction execution

is also reduced in cases where there is a delay in the supply of instructions, such as internal conflict of bus

in the CPU, instruction execution through external bus interface etc.

Normally, instructions are executed sequentially in the integer pipeline. For example, if instruction A enters

the pipeline before instruction B, it invariably reaches WB stage before instruction B. However, when the

register used in Load instruction (LD instruction) is not used in the subsequent instruction, the subsequent

instruction is executed before the completion of execution of load instruction based on the non-blocking

loading buffer.

Figure 5.1-2 Example of integer pipeline operation (2)

MA stage is prolonged in case of Load instruction (LD instruction) till the completion of reading of the

loaded data. However, the subsequent instruction is executed as it is, if the register used in the load

instruction is not used in the subsequent instruction.

In the Example given in Figure 5.1-1, loading is carried out in R1 (load value is written in R1) based on

preceding LD instruction, and R1 contents are referred to in the subsequent CMP instruction. Since the

loaded data returns in 1 cycle, execution of instructions is sequential.

Similarly in the Example given in Figure 5.1-2, R1 that writes load value with LD instruction is used in the

CMP instruction. Since the loaded data does not return in 1 cycle, execution till LDI:8 instruction is carried

out and CMP instruction is made to wait at the ID stage by register hazard.

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

LD @R10, R1

(Example 1)

LDI:8 #0x02, R2

CMP R1, R2

BNE:D Label_G

ADD #0x1, R1

IF ID EX MA MA MA WB

IF ID EX MA WB

IF ID ID ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

LD @R10, R1

LDI:8 #0x02, R2

CMP R1, R2

BNE:D Label_G

ADD #0x1, R1

(Example 2)