FR81 Family

102 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 6 INSTRUCTION OVERVIEW

6.6

DIV0S R2 ; divisor in R2

DIV1 R2 ; #1

DIV1 R2 ; #2

. . .

DIV1 R2 ; #30

DIV1 R2 ; #31

DIV1 R2 ; #32

Division result is stored in the following registers.

• Multiplication/Division Register (MDL): quotient of unsigned 32 bit

• Multiplication/Division Register (MDH): remainder of unsigned 32 bit

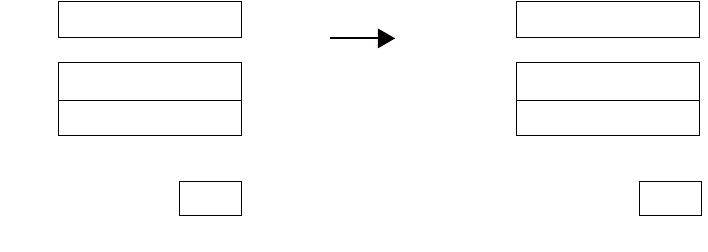

Example of execution of unsigned division has been indicated in Figure 6.6-2.

Figure 6.6-2 Example of execution of unsigned division

In SOFTUNE Assembler, DIVU Instruction has been arranged to carry out unsigned division as Assembler

Pseudo Machine Instruction. Using this DIVU Instruction in place of above mentioned 33 Instructions,

unsigned division can be described with 1 Instruction. See "FR family SOFTUNE Assembler Manual" for

DIVU Instruction.

MDH

MDL

D1 D0 T

SCR SCR

××0

D1 D0 T

000

R2

0123 4567

MDH

MDL

R2

000000E0

00000078

FEDCBA98

××××××××

Before execution After execution

0123 4567