FR81 Family

44 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 4 RESET AND "EIT" PROCESSING

4.2

4.2.2 EIT Processing Sequence

FR81 family CPU processes EIT events as follows.

1. The vector table indicated by the table base register (TBR) and the offset value of the vector number

corresponding to the particular EIT are used to determine the entry address for the processing program

for the EIT.

2. For restarting, the contents of the old program counter (PC) and the old program status (PS) are saved to

the stack area designated by the system stack pointer (SSP).

3. "0" is saved in the stack flag (S). Also, the interrupt level Mask Register (ILM) and interrupt enable flag

(I) are updated through EIT.

4. Entry address is saved in the program counter (PC).

5. After the processing flow is completed, just before the execution of the instruction in the entry address,

the presence of new EIT sources is determined.

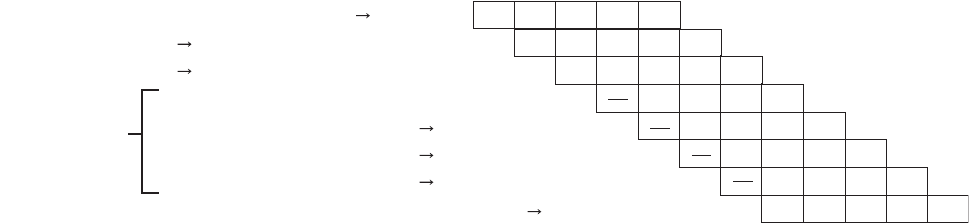

Figure 4.2-1 shows the operations in the EIT processing sequence.

Figure 4.2-1 Operations in EIT Processing Sequence

Vector tables are located in the main memory, occupying an area of 1 Kbyte beginning with the address

shown in the table base register (TBR). This area is used as a table of entry addresses for EIT processing.

For details on vector tables, refer to "2.1.2 Vector Table Area" and "3.3.6 Condition Code Register

(CCR)".

Regardless of the value of stack flag (S), the program status (PS) and program counter (PC) is saved in the

stack pointed to by the system stack pointer (SSP). After an EIT processing has commenced, the program

counter (PC) is saved in the address pointed to by the system stack pointer (SSP), while the program status

(PS) is saved at address 4 plus the address pointed to by the system stack pointer (SSP).

Figure 4.2-2 shows an example of saving program counter (PC) and program status (PS) during the

occurrence of an EIT event.

Instruction at which EIT event is detected

Canceled instruction

EIT sequence

(1) Vector address calculation and new PC setting

(2) SSP update and PS save

(3) SSP update and PC save

(4) Detection of new EIT event

First instruction in EIT handler sequence (branching instruction)

Canceled instruction

IF ID EX MA WB

IF ID EX MA PC

ID(1) EX(1) MA(1) WB(1)

IF ID xxxx xxxx xxxx

IF xxxxxxxx xxxx xxxx

ID(2) EX(2) MA(2) WB(2)

ID(3) EX(3) MA(3) WB(3)

ID(4) EX(4) MA(4) WB(4)