FR81 Family

78 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 5 PIPELINE OPERATION

5.5

5.5 Delayed branching processing

Because FR81 Family CPU features pipeline operation, the loading of the instruction is

already completed at the time of execution of branching instruction. The processing

speeds can be improved by using the delayed branching processing.

5.5.1 Example of branching with non-delayed branching

instructions

Non-delayed branching instruction executes instructions in the order of program but the execution speed

drops down by 1 cycle as compared to delayed branching instruction when branching.

In a pipeline operation, by the time the CPU recognizes an instruction as a branching instruction the next

instruction has already been loaded. To process the program as written, the instruction following the

branching instruction must be cancelled in the middle of execution. Branching instructions that are handled

in this manner are non-delayed branching instructions.

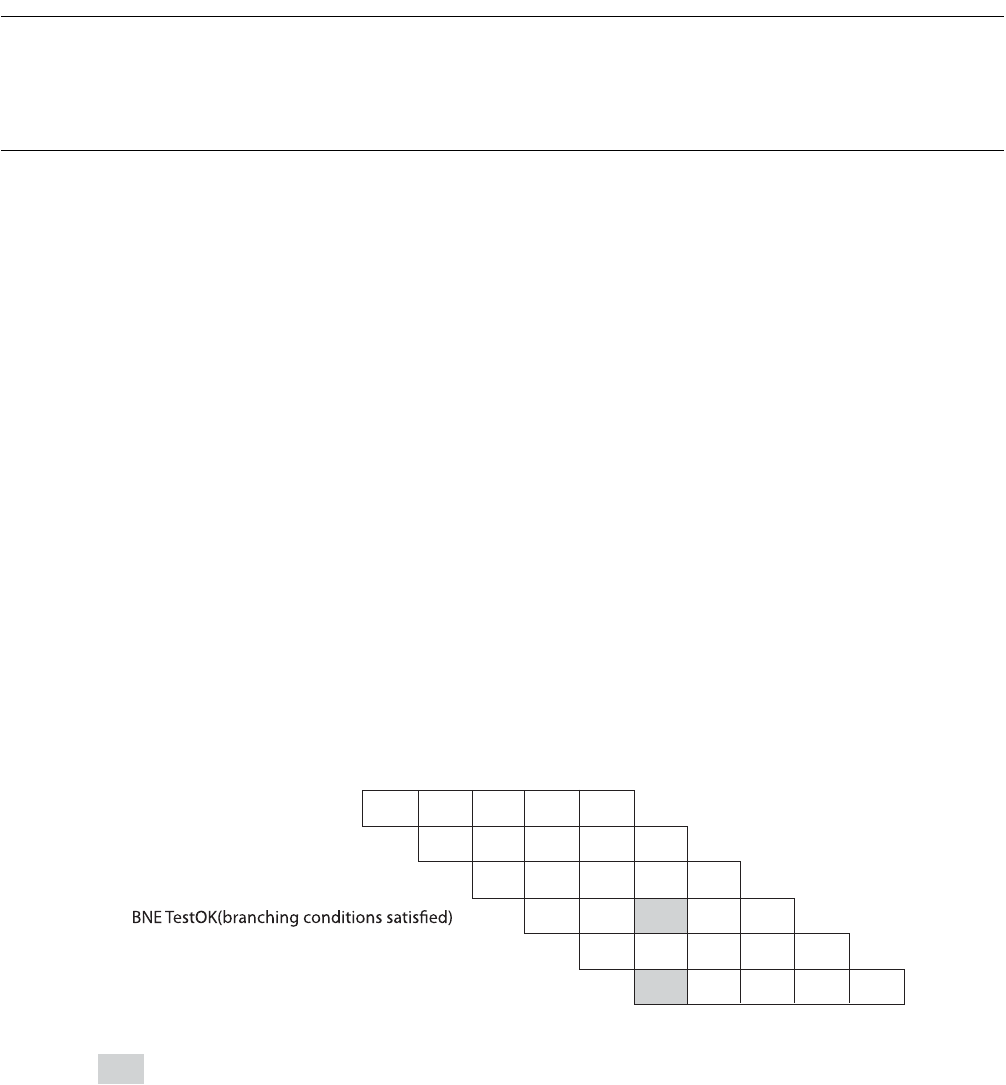

The example of processing non-delayed branching instruction with fulfilled branching conditions is given

in Figure 5.5-1 which shows that execution of the "ST R2,@R12" instruction (instruction placed

immediately after branching instruction) that had started pipeline operation before fetching instruction from

the branching destination is cancelled in the middle. Due to this, program processing happens as the

program is written, but branching instruction apparently takes 2 cycles for completion.

Figure 5.5-1 Example of processing of Non-Delayed Branching instruction

(Branching conditions satisfied)

Figure 5.5-2 shows an example of processing a non-delayed branching instruction when branching

conditions are not fulfilled. In this example, the "ST R2,@R12" instruction (instruction kept immediately

after branching instruction) that started pipeline processing before fetching instruction from the branching

destination is executed without being cancelled. The processing of program happens as written in the

program since the instructions are executed sequentially, without branching, and branching instruction

execution speed is apparently of 1 cycle.

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF -- -- -- --

-- : Canceled stages

: PC change

IF ID EX MA WB

LD @R10, R1

LD @R11, R2

ADD R1, R3

ST R2, @R12(instruction immediately a

f

ter)

ST R2, @R13(branch destination instruction)