CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 319

FR81 Family

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.118

7.118 LDUH (Load Halfword Data in Memory to Register)

Loads the half word data at memory address BP+u16 × 2 to Ri. Unsigned u16 value is

calculated. The value in u16 × 2 is specified as udisp17.

● Assembler Format

LD @(BP, udisp17), Ri

● Operation

(BP+u16 × 2) → Ri

● Flag Change

N, Z, V, C: Unchanged.

● Classification

Memory Load instruction, FR81 family

● Execution Cycles

a cycle

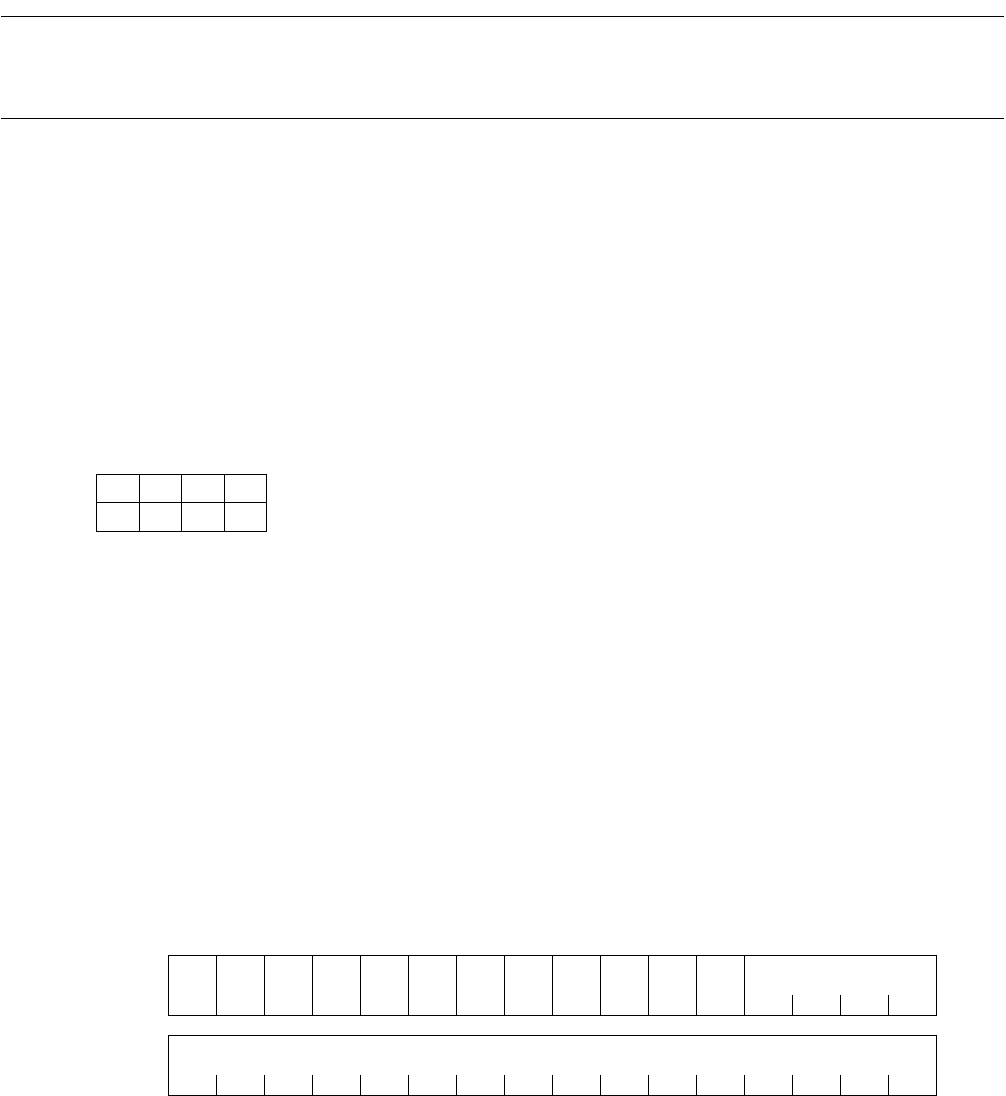

● Instruction Format

● EIT Occurrence and Detection

A data access protection violation exception, an invalid instruction exception (data access error), or an

interrupt is detected.

NZVC

----

MSB LSB

(n+0)000001110101 Ri

(n+2) u16