FR81 Family

54 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 4 RESET AND "EIT" PROCESSING

4.5

Figure 4.5-1

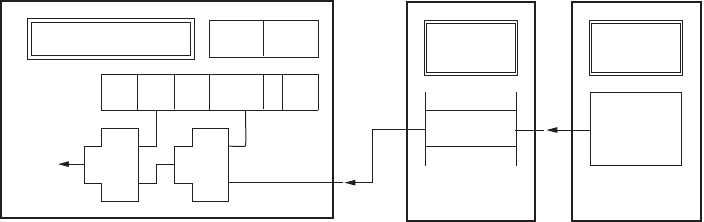

Acceptance Procedure of General Interrupts

Each interrupt request is assigned an interrupt level by the interrupt controller, and it is possible to mask

requests according to their level values. Also, it is possible to disable all interrupts by using the interrupt

enable flag (I) in the condition code register (CCR).

When interrupt requests are generated by peripheral functions, they can be accepted under the following

conditions.

• The level of interrupt level mask register (ILM) is higher (i.e. the numerical value is smaller) than the

interrupt level set in the interrupt control register (ICR) corresponding to the vector number

• The interrupt enable flag (I) in the condition code register (CCR) is set to “1”

Interrupt control register (ICR) is a register of interrupt controller. Refer to the hardware manual of various

models for details about the interrupt controller.

The following operations are performed after a general interrupt is accepted.

1. Transition to privilege mode is carried out, the stack flag (S) is cleared, and the accepted interrupt

request level is set to the interrupt level mask register (ILM).

"0" → UM "0" → S Interrupt level → ILM

2. The contents of the program status (PS) are saved to the system stack.

SSP - 4 → SSP PS → (SSP)

3. The address of the instruction next to that accepted a general interrupt is saved to the system stack.

SSP - 4 → SSP next instruction address → (SSP)

4. The program counter (PC) value is updated by referring to the vector table.

(TBR + Offset) → PC

5. A new EIT event is detected.

When using general interrupts, it is required to set the interrupt level in the interrupt control register (ICR)

corresponding to the vector number of the interrupt controller. Also perform the settings of the various

peripheral functions and interrupt enable. Refer to the hardware manual of each model for details on

interrupt controller and various peripheral functions.

FR81 family CPU SSPUSP

PS I ILM S

INT

AND

compare

Interrupt

controller

Peripheral

device

ICR#n

Interrupt

enable bit

request