FR81 Family

42 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 4 RESET AND "EIT" PROCESSING

4.1

4.1 Reset

A reset forcibly terminates the current process, initializes the device, and restarts the

program from the reset vector entry address.

The reset process is executed in privilege mode. Transition to user mode should be

carried out by executing a RETI instruction.

When a reset is generated, CPU terminates the processing of the instruction execution at that time and goes

into inactive status until the reset is cancelled. When the reset is cancelled, the CPU initializes all internal

registers and starts execution beginning with the program indicated by the new value of the program

counter (PC).

Reset processing has a higher priority level than each operation of the EIT processing described later. Reset

is accepted even in between an EIT processing.

When a reset is generated, FR81 family CPU makes an attempt to initialize each register, but all registers

cannot be initialized. Each register sets a value through the program executed after a reset, and uses it.

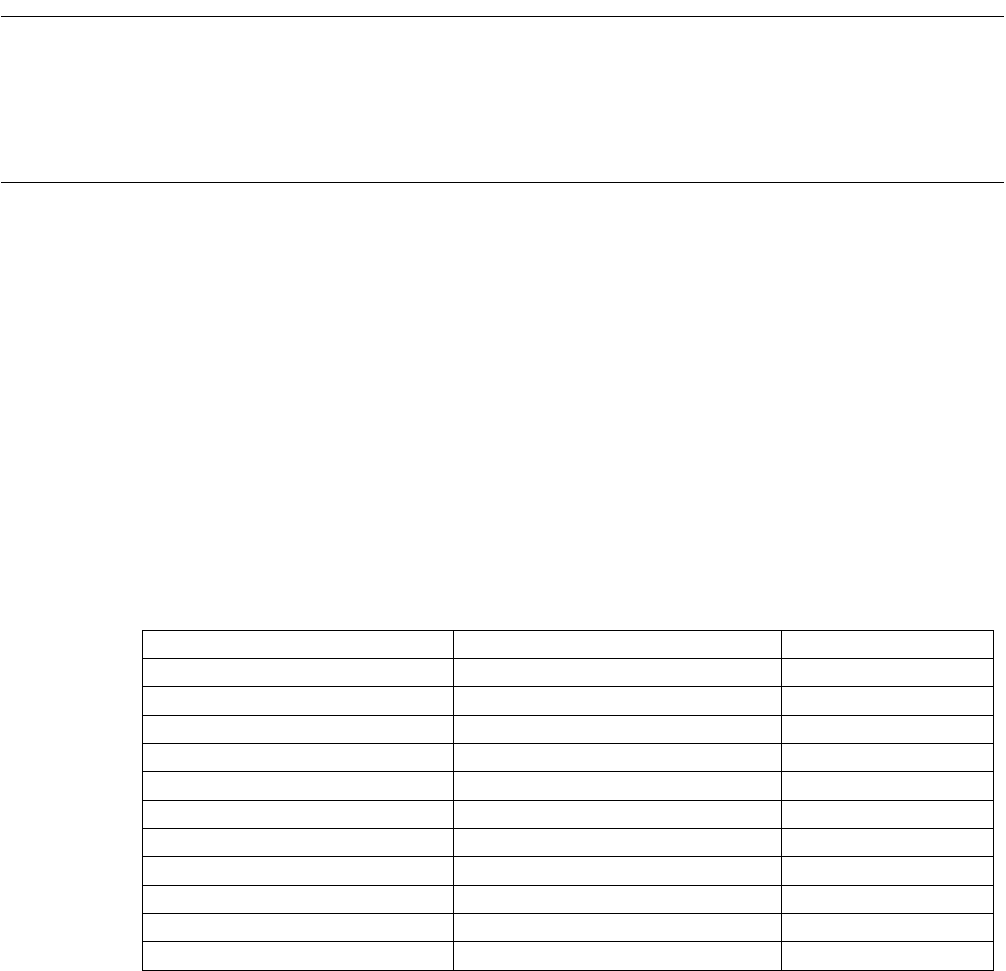

Table 4.1-1 shows the registers that are initialized following a reset.

Table 4.1-1 Registers that are initialized following a reset

For details of My computer built-in functions (peripheral devices, etc.) following a reset, refer to the

Hardware Manual provided with each device.

Register Initial Value Remarks

Program counter (PC)

Word data at location 000F FFFC

H

Reset vector

Interrupt level mask register (ILM)

15(01111

B

)

Step trace trap flag (T) “0” Trace OFF

Interrupt enable flag (I) “0” Interrupt disabled

Stack flag (S) “0” Use SSP

Table base register (TBR)

000F FC00

H

System stack pointer (SSP)

0000 0000

H

Debug state flag (DBG)

“0”

No debug state

User mode flag (UM)

“0”

Privilege mode

Exception status register (ESR)

0000 0000

H

General-purpose register R15 SSP As per stack flag (S)