CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 135

FR81 Family

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.16

7.16 ASR2 (Arithmetic shift to the Right Direction)

Makes an arithmetic right shift of the word data in Ri by u4+16 bits, stores the result to

Ri.

● Assembler Format

ASR2 #u4, Ri

● Operation

Ri >> {u4 + 16} → Ri

● Flag Change

N: Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z: Set when the operation result is zero, cleared otherwise.

V: Unchanged.

C: Holds the bit value shifted last.

● Classification

Shift instruction, Instruction with delayed slot

● Execution Cycles

1 cycle

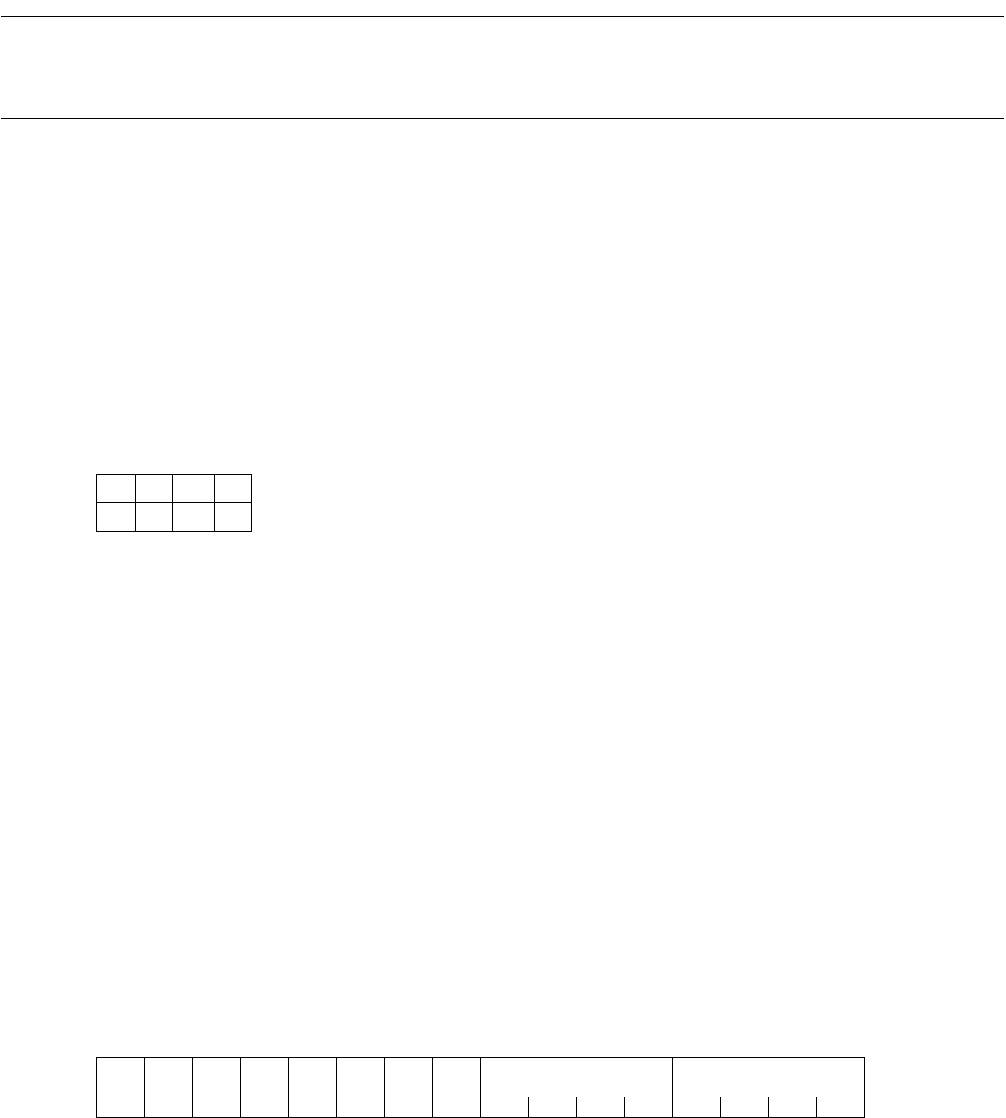

● Instruction Format

NZVC

CC - C

MSB LSB

10111001 u4 Ri