CM71-00105-1E FUJITSU MICROELECTRONICS LIMITED 141

FR81 Family

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.19

7.19 Bcc (Branch relative if Condition satisfied)

This is a branching instruction without a delay slot. If the conditions specified for each

instruction are satisfied, branch to the address indicated by label9 relative to the value

of the program counter (PC). When calculating the address, double the value of rel8 as

a signed extension. If conditions are not satisfied, no branching occurs.

● Assembler Format

BRA label9 BV label9

BNO label9 BNV label9

BEQ label9 BLT label9

BNE label9 BGE label9

BC label9 BLE label9

BNC label9 BGT label9

BN label9 BLS label9

BP label9 BHI label9

● Operation

if (condition) then

PC + 2 + exts(rel8 × 2) → PC

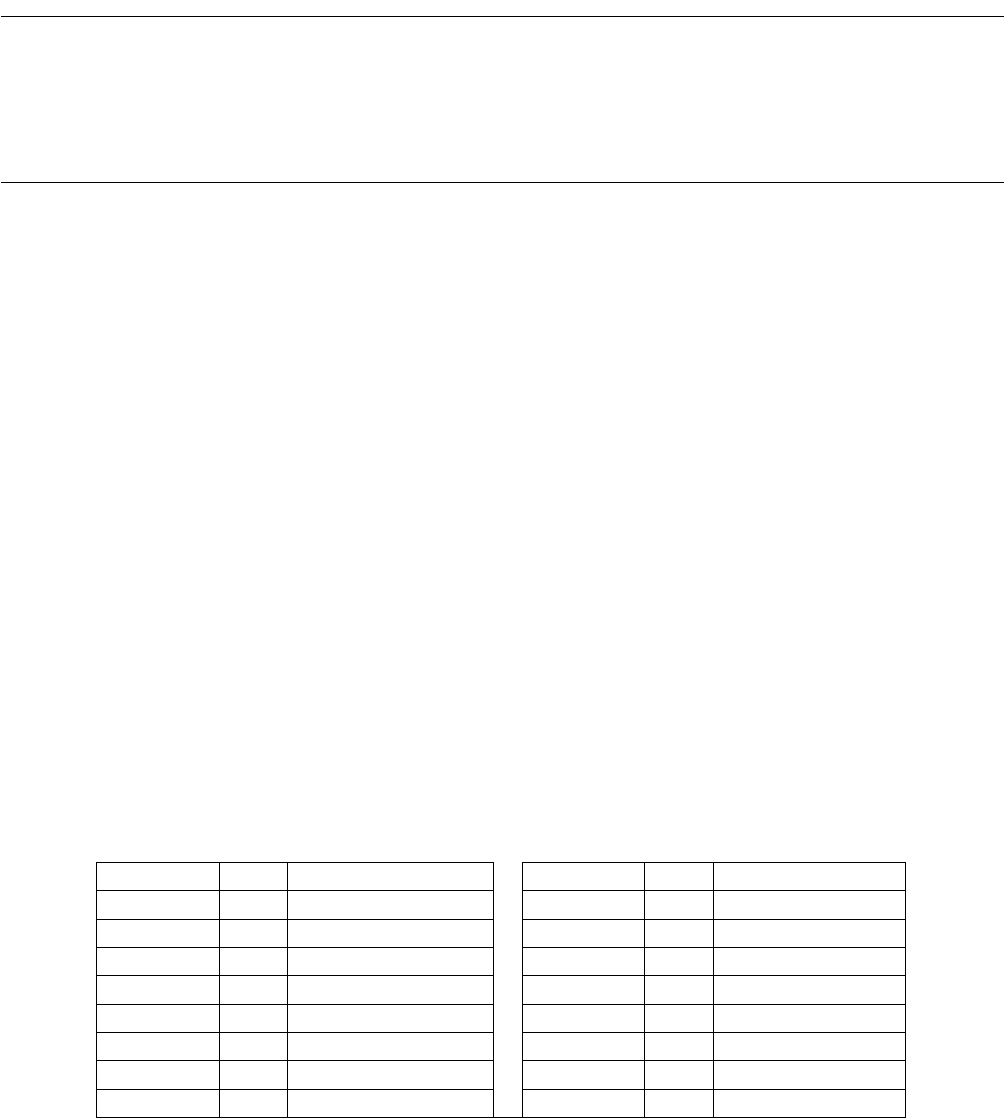

Branching of each instruction is shown in Table 7.19-1.

Table 7.19-1 Branching conditions

Mnemonic cc Condition Mnemonic cc Condition

BRA 0000 Always satisfied BV 1000 V == 1

BNO 0001 Always unsatisfied BNV 1001 V == 0

BEQ 0010 Z == 1 BLT 1010 (V ^ N) == 1

BNE 0011 Z == 0 BGE 1011 (V ^ N) == 0

BC 0100 C == 1 BLE 1100 ((V ^ N) | Z) == 1

BNC 0101 C == 0 BGT 1101 ((V ^ N) | Z) == 0

BN 0110 N == 1 BLS 1110 (C | Z) == 1

BP 0111 N == 0 BHI 1111 (C | Z) == 0

| : Logical add (or) ^ : Exclusive-OR (exor) ==: comparison operation (satisfied by congruence)