FR81 Family

248 FUJITSU MICROELECTRONICS LIMITED CM71-00105-1E

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.76

7.76 FLDM (Single Precision Floating Point Data Load to

Multiple Register)

The registers shown on the frlist are sequentially restored from the stack. Registers

FR0 to FR15 can be set on the frlist. They are processed in ascending order of register

numbers.

● Assembler Format

FLDM (frlist)

● Operation

The following operations are repeated according to the number of registers specified in the parameter frlist.

(R15) → FRi

R15 + 4 → R15

The bit and register relation of frlist of FLDM instruction is shown in Table 7.76-1.

● Classification

Floating point instruction, FR81 family

● Execution Cycles

na cycle (n: Transfer register number)

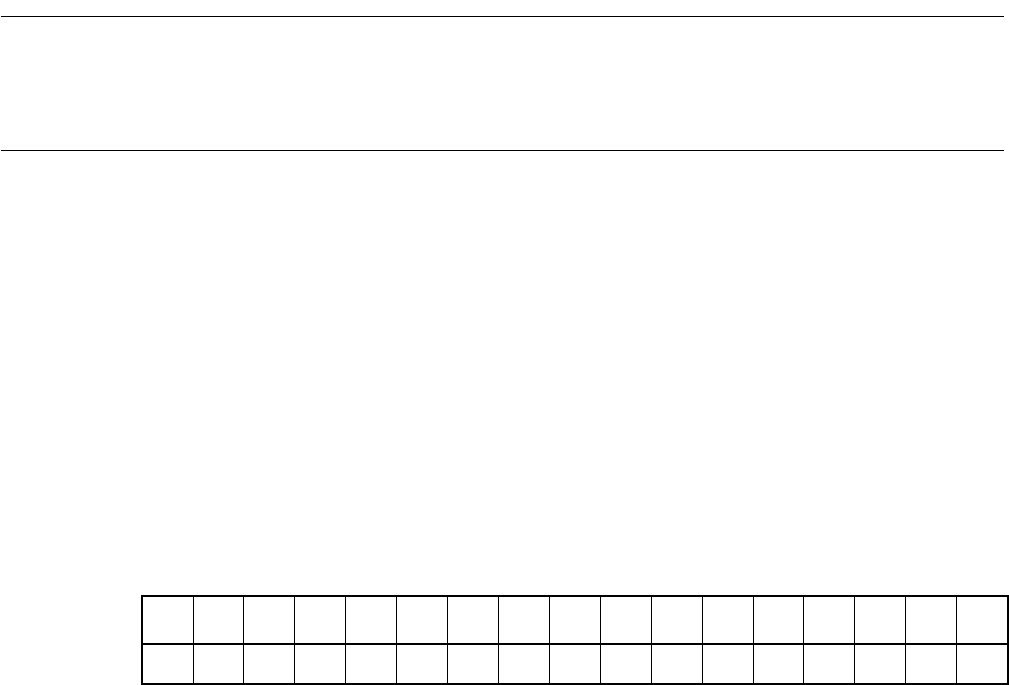

Table 7.76-1 The bit and register relation of frlist of FLDM instruction

bit1514131211109876543210

FRi FR15 FR14 FR13 FR12 FR11 FR10 FR9 FR8 FR7 FR6 FR5 FR4 FR3 FR2 FR1 FR0