85C220

CLOCK &

"ESET

GENERATOR

CLK

RESET

CLK2

I T

RESET

CLK2 J

ADS#

INT"

-

-

-

NA#

M/IO#

W/R#

D/C

-

0>

ell

-

-

~~Y

READY#

-

1386'· DX

CPU

READY

AS

~

A3

74F138

A12-A20

ADDRESS

BUS

8EO#

8E1#

8516#

A

DOo015

DATA

BUS

'I

~"DY~

IOPLD1

IOPLD2

CLK2

CLK2

-

CLK

- CLK

WICNTO

-

NA

TRtOEN

-

ADS

WTCHT'

-

MIlO

-

READY

WTCNT2

-

WI"

INTA

INTA

-

P20RB

D/C

EPRD

EPRDY

-

A3.

IOWR

IOWA

PlRECYC

-

TlMEDLY

lORD

lORD

BUSCYC

-

BUSCYC

RECV

RECY

ALEIO

-

-

CS1WS

nUEDLY

-

~

- CS3WS

CSSWS

-

"

ALE#

ADDRESS

BUS

r

74F373

LATCHES

A1-A15

.....-

x.

-

OT/R#

DEN#

"

74F245

TRANSCElVER

TO

DATA

BUS

r

x.

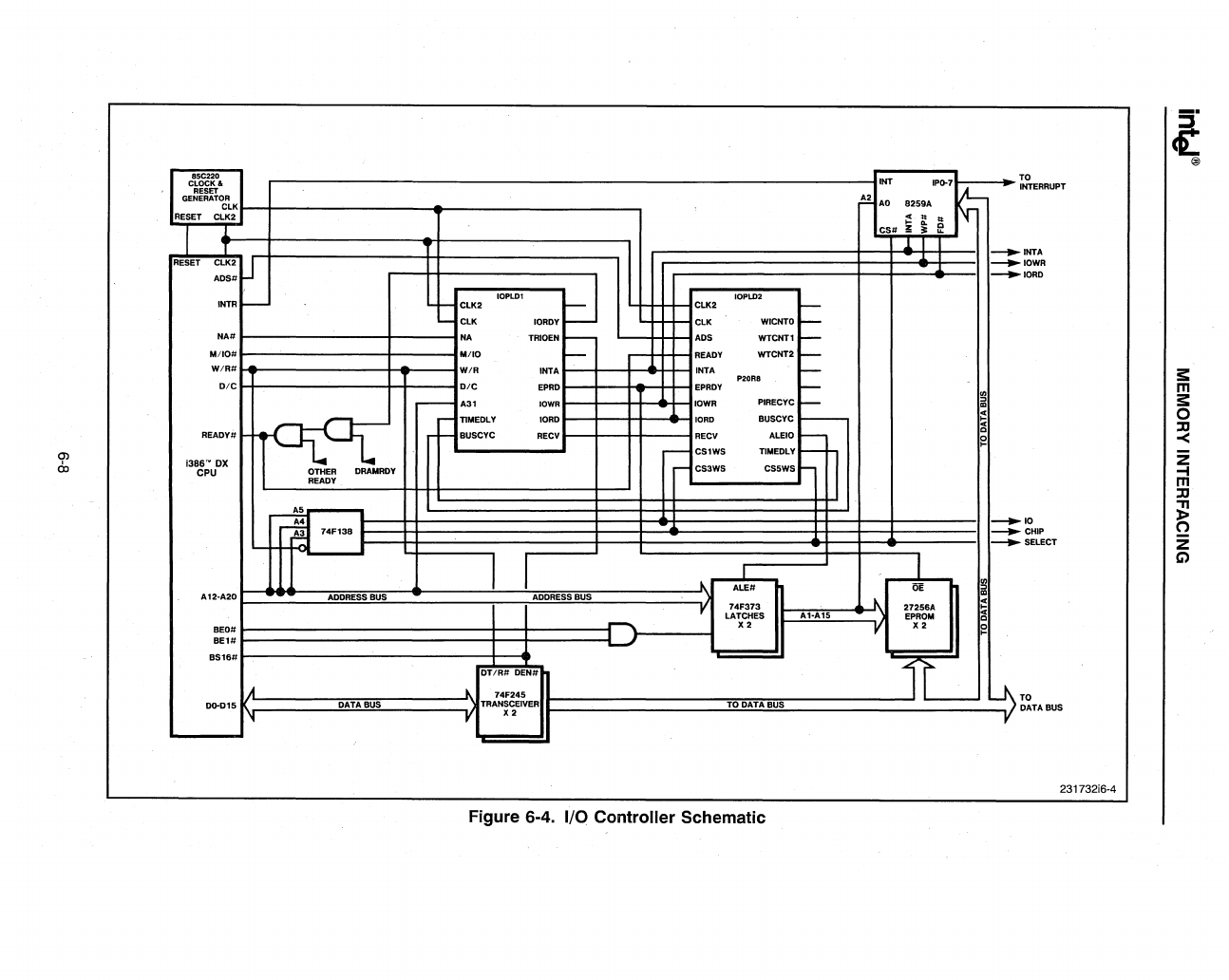

Figure 6-4.

I/O

Controller Schematic

INT IP0-7

ft-

~

AD

8259A

'f

cs#~I~

In

iii

i

g

I

ijE

..

"

ID

~

C

27256A

~

EPROM

V'

X.

g

11

TO

INTERRUPT

_INTA

_IOWR

_lORD

-~

_ClOP

:_SELECT

TO

~

DATA

BUS

V'

231732i6-4

l

s::

m

s::

o

~

Z

-I

m

:::D

~

Z

G)

®