ClK2

ClK

DEN#

DT/R#

MEMORY INTERFACING

READ BANK 0

T

2

P

WRITE BANK 1

DATA

BUS

(PROCESSOR SIDE)

_._D_A_TA_B_U_FF_ER_D-tR~IVI_NG

___

::i

80386

DRIVING

CAS#

DATA

BUS

(DRAM SIDE)

-----f----.JI

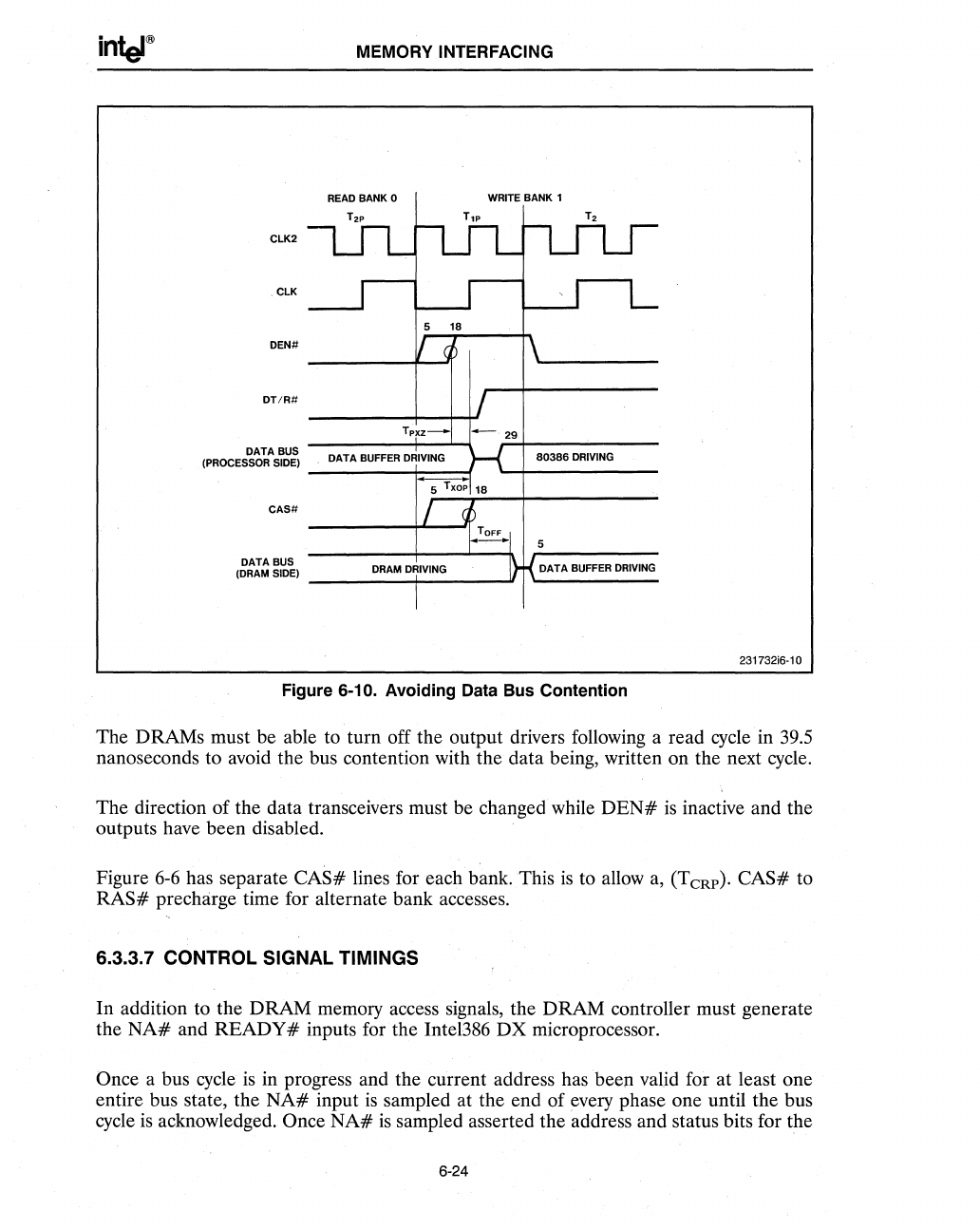

Figure 6-10. Avoiding Data Bus Contention

231732i6-10

The DRAMs must be able to turn off the output drivers following a read cycle in

39.5

nanoseconds to avoid the bus contention with the data being, written on the next cycle.

The direction of the data transceivers must be changed while

DEN#

is

inactive and the

outputs have been disabled.

Figure

6-6

has separate

CAS#

lines for each bank.

This

is

to allow

a,

(T

CRP)'

CAS#

to

RAS#

precharge time for alternate bank accesses.

6.3.3.7 CONTROL SIGNAL TIMINGS

In addition to the DRAM memory access signals, the DRAM controller must generate

the

NA#

and READY # inputs for the Intel386

DX

microprocessor.

Once a bus cycle

is

in progress and the current address has been valid for at least one

entire bus state, the

NA#

input

is

sampled at the end of every phase one until the bus

cycle

is

acknowledged. Once

NA#

is

sampled asserted the address and status bits for the

6-24