lOCAL

BUS

INTERFACE

CLK2

[

RES#

[~'----------5S

5

mml

THE

CLOCK

GENERATOR

ENSURES

THAT

ITS

RESET

OUTPUT

FALLING

EDGE

OCCURS

DURING

PHASE

lWO

RESET

[

____

--1/,.-------SS

5-5

------

.....

{'--

____

_

1386

N

ox

CPU

ASSUMES

RESET

FALLING

EDGE

OCCURS

DURING

PHASE

lWO,

AND

SETS

ITS

OWN

INTERNAL

PHASE

TO

MATCH

231732i3-21

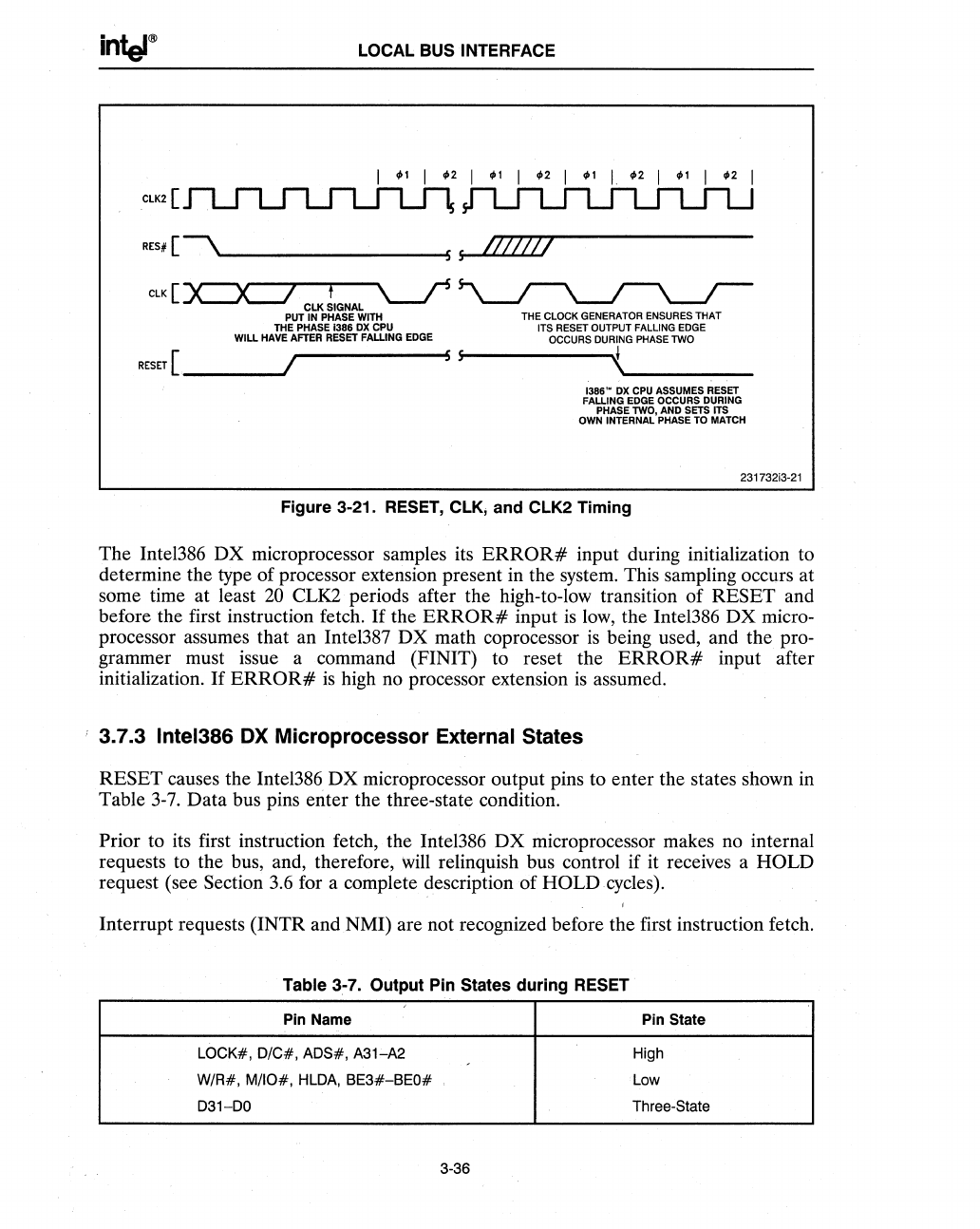

Figure 3-21.

RESET,

ClK;

and

ClK2

Timing

The Intel386 DX microprocessor samples its

ERROR#

input during initialization to

determine the type of processor extension present in the system. This sampling occurs at

some time at least

20

CLK2 periods after the high-to-Iow transition of RESET and

before the first instruction fetch.

If

the

ERROR#

input

is

low,

the Intel386

DX

micro-

processor assumes that an Intel387 DX math coprocessor

is

being used, and the pro-

grammer must issue a command (FINIT) to reset the

ERROR#

input after

initialization.

If

ERROR#

is

high no processor extension

is

assumed.

3.7.3 Intel386

OX

Microprocessor External States

RESET causes the Inte1386 DX microprocessor output pins to enter the states shown in

Table

3-7.

Data bus pins enter the three-state condition.

Prior to its first instruction fetch, the Inte1386

DX

microprocessor makes no internal

requests to the bus, and, therefore,

will

relinquish bus control if it receives a HOLD

request (see Section 3.6 for a complete description of HOLD cycles).

Interrupt requests (INTR and NMI) are not recognized before the first instruction fetch.

Table 3-7. Output Pin States during

RESET

Pin Name Pin State

LOCK#, O/C#, AOS#, A31-A2 High

W/R#, M/IO#,

HLOA,

BE3#-BEO# Low

031-00

Three-State

3-36