LOCAL BUS INTERFACE

BUB

States:

ALWAYS

READY

#

ASSERTED·

REQUEST

PENDING

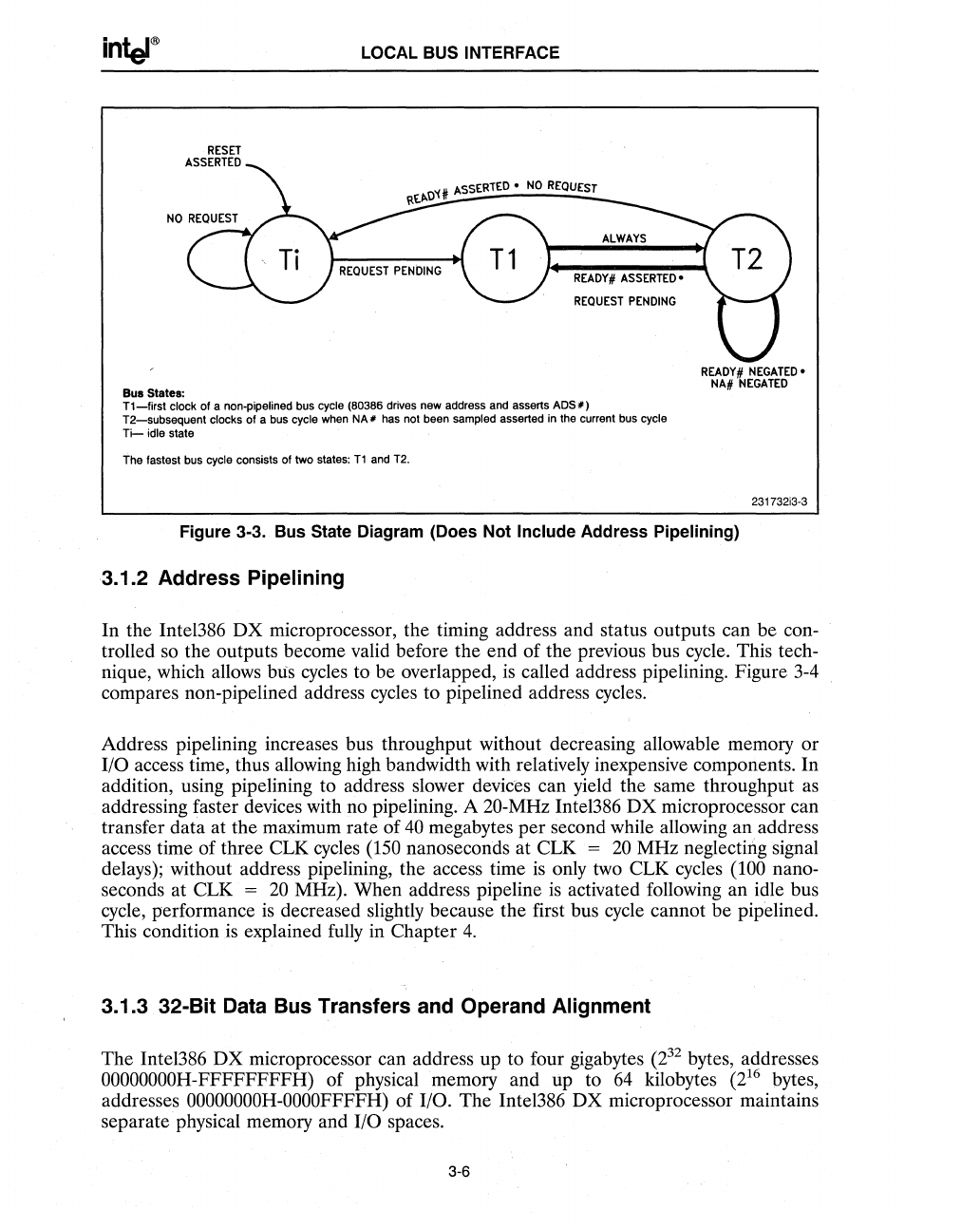

T1-first

clock of a non-pipelined bus cycle (80386 drives new address

and

asserts

ADS")

T2-subsequent clocks of a

bus

cycle when

NA"

has

not been sampled asserted

in

the

current

bus

cycle

H-

idle state

The fastest bus

cycle consists of two states:

T1

and

T2.

READY#

NEGATED·

NA#

NEGATED

231732i3-3

Figure 3-3. Bus State Diagram (Does Not Include Address Pipelining)

3.1.2 Address Pipelining

In

the Intel386

OX

microprocessor, the timing address and status outputs can be con-

trolled

so

the outputs become valid before the end of the previous bus

cycle_

This tech-

nique, which allows bus cycles to be overlapped,

is

called address pipelining. Figure

3-4

compares non-pipelined address cycles to pipelined address cycles.

Address pipelining increases bus throughput without decreasing allowable memory or

I/O access time, thus allowing high bandwidth with relatively inexpensive components. In

addition, using pipelining to address slower devices can yield the same throughput

as

addressing faster devices with no pipelining. A 20-MHz Intel386

OX

microprocessor can

transfer data at the maximum rate of

40

megabytes per second while allowing an address

access time of three CLK cycles

(150 nanoseconds at CLK =

20

MHz neglecting signal

delays); without address pipelining, the access time

is

only two CLK cycles (100 nano-

seconds at CLK =

20

MHz). When address pipeline

is

activated following an idle bus

cycle, performance

is

decreased slightly because the first bus cycle cannot be pipelined.

This condition

is

explained

fully

in Chapter

4.

3.1.3 32-Bit Data Bus Transfers and Operand Alignment

The Inte1386

OX

microprocessor can address up to four gigabytes (2

32

bytes, addresses

OOOOOOOOH-FFFFFFFFH)

of physical memory and up to

64

kilobytes (2

16

bytes,

addresses

OOOOOOOOH-OOOOFFFFH)

of I/O. The Intel386

OX

microprocessor maintains

separate physical memory and

I/O spaces.

3-6