MEMORY INTERFACING

• The choice of chip-select logic in the design

is

arbitrary. Other DRAM memory-

mapping schemes can be implemented

by

modifying the address decoding to the

DRAM State

PLD

chip-selects.

.•

It

is

possible to deassert

RAS#

before the end of the cycle to improve the

RAS#

precharge time .

• For a single

DRAM

bank rather than two, the user should tie the

DRAMPI

PLD A2

input low, leave RASI # unconnected (only RASO#

is

used), and feed the Intel386

DX

microprocessor address bit A2 into the address multiplexer. The

DRAMPI

PLD

equations can be modified to change the RASI # output to duplicate the RASO#

output for more drive capability, and the A2 input can be used as another chip-select

input. When only one bank

is

used, no accesses can be interleaved, and back-to-back

accesses run with three wait states with the 3-CLK design (independent of address

pipelining).

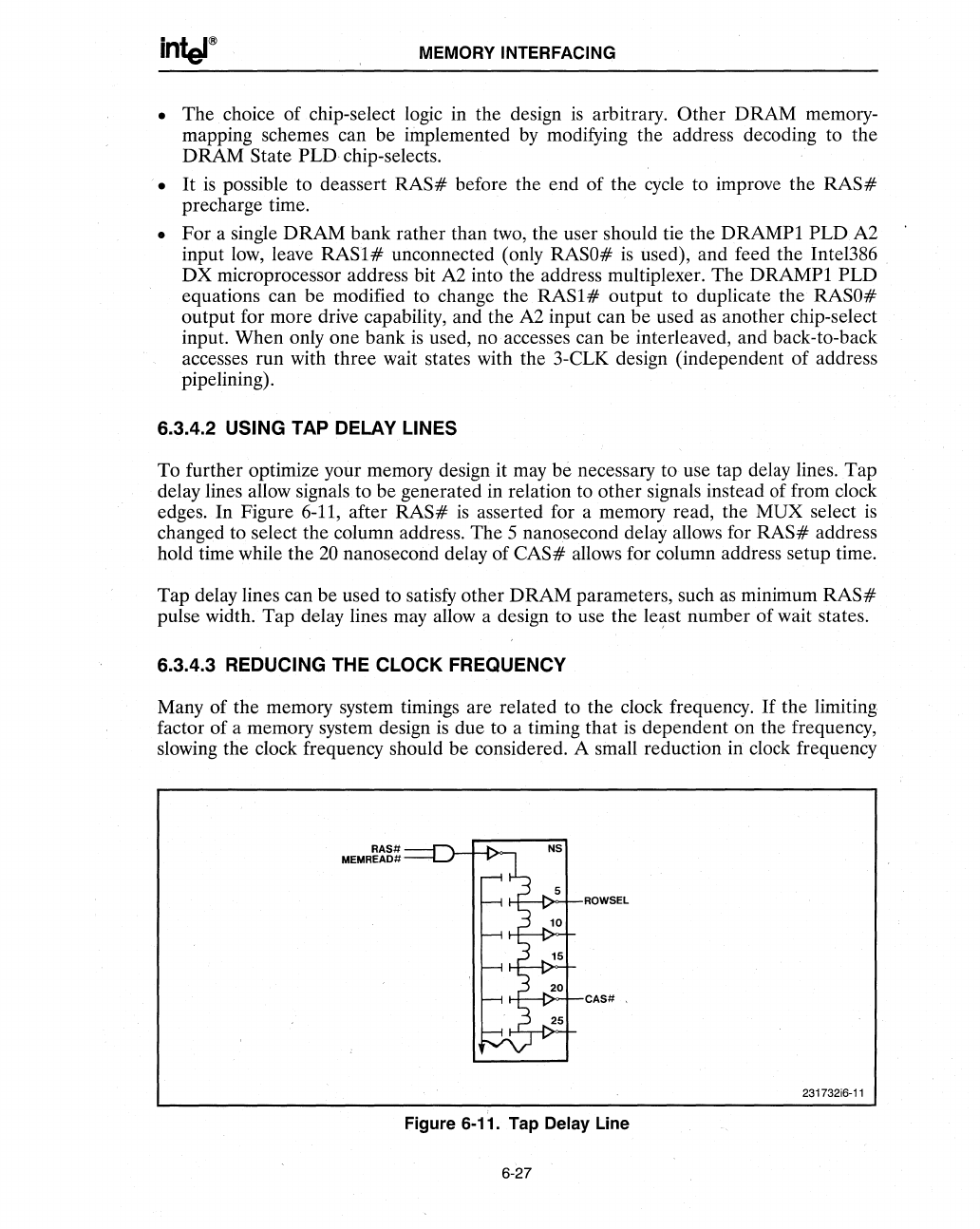

6.3.4.2 USING TAP DELAY LINES

To further optimize your memory design

it

may be necessary to use tap delay lines. Tap

delay lines allow signals to be generated in relation to other signals instead of from olock

edges. In Figure

6-11,

after

RAS#

is

asserted for a memory read, the MUX select

is

changed to select the column address. The 5 nanosecond delay allows for

RAS#

address

hold time while the

20

nanosecond delay of

CAS#

allows for column address setup time.

Tap delay lines can be used to satisfy other

DRAM

parameters, such as minimum

RAS#

pulse width. Tap delay lines may allow a design to use the

le,!-st

number of wait states.

6.3.4.3 REDUCING THE CLOCK FREQUENCY

Many of the memory system timings are related to the clock frequency.

If

the limiting

factor of a memory system design

is

due to a timing that

is

dependent on the frequency,

slowing the clock frequency should be considered. A small reduction in clock frequency

RAS#

NS

MEMREAD#

5

ROWSEL

10

15

20

CAS#

25

231732i6-11

Figure 6-11. Tap Delay Line

6-27