CACHE SUBSYSTEMS

31

32·BIT

PROCESSOR

ADDRESS

SELECT

INDEX

INDEX

TAG

FFFC

01

FFF8 FF

0010

OOOC

0008

00

0004

01

0000

00

(14 BITS)

I_

-I

15 BYTES

64KSRAM

!-64K

CACHE=16

BITS-!

I-:z

GIGABYTE

DRAM

= 31

BYTES~

DATA INDEX

FFFC

11223344 FFF8

0010

DATA

OOOC

12345678

~

11223344

OOOS

0004

0000

-

-

-

87654321

~

~

11235813

12345678

13579246

-

FFFC

FFF8

j+32BITS+j

0010

OOOC

0.008

CACHE

'--+

11235813

0004

0000

FFFC

FFF8

0010

OOOC

87654321

0008

0004

13579246

0000

j+32BITS+j

TAG

l~~

1-'

)-

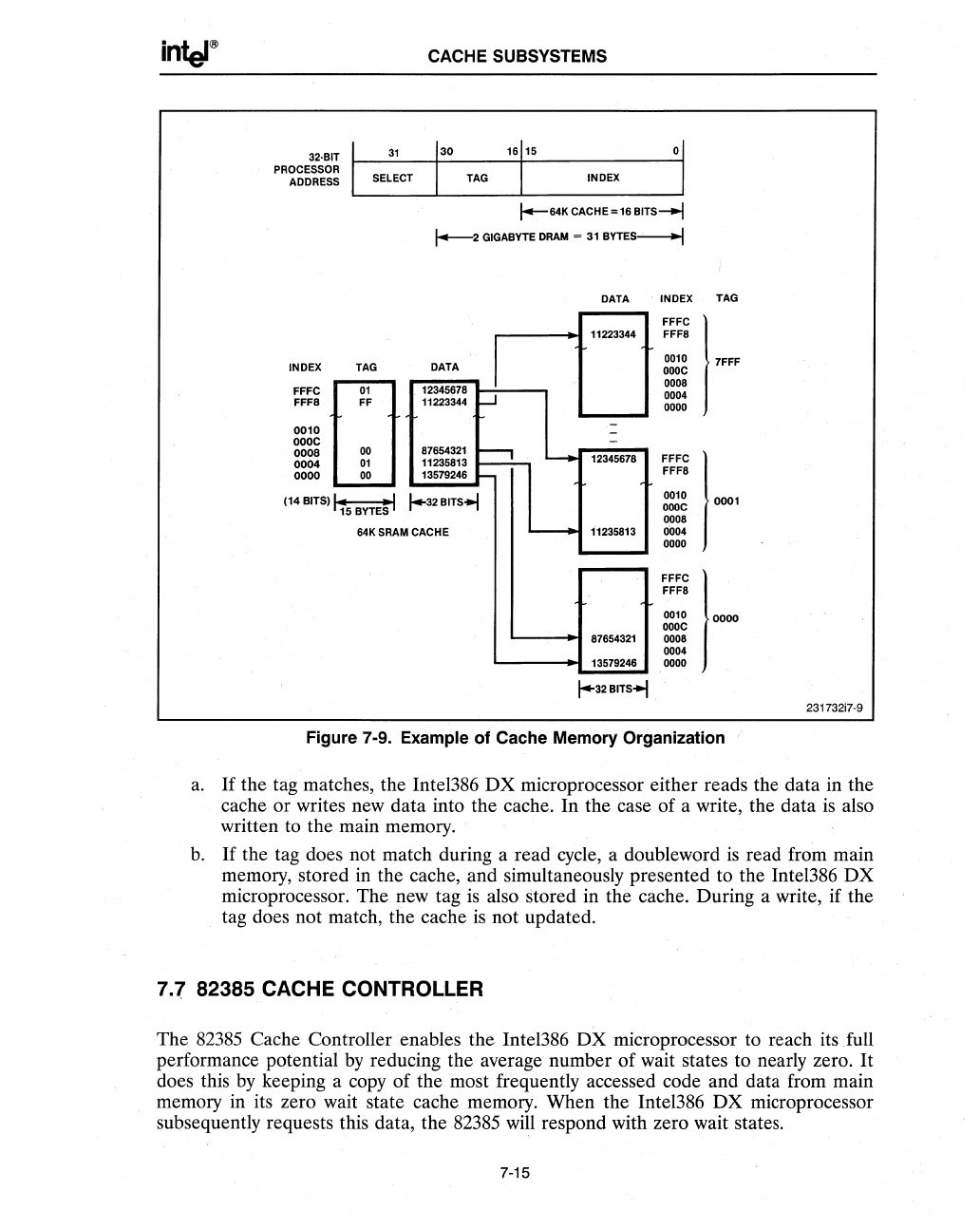

Figure 7-9. Example of Cache Memory Organization

231732i7·9

a.

If

the tag matches, the Intel386 DX microprocessor either reads the data in the

cache or writes new data into the cache. In

the

case of a write, the data

is

also

written to the main memory.

b.

If

the tag does not match during a read cycle, a doubleword

is

read from main

memory, stored in the cache, and simultaneously presented to the Intel386

DX

microprocessor. The new tag

is

also stored in the cache. During a write, if the

tag does not match, the cache

is

not updated.

7 . ., 82385 CACHE CONTROLLER

The

82385

Cache Controller enables the Inte1386 DX microprocessor to reach its full

performance potential

by

reducing the average number of wait states to nearly zero.

It

does this

by

keeping a copy of the most frequently accessed code and data from main

memory in its zero wait state cache memory. When the Intel386 DX microprocessor

subsequently requests this data, the

82385

will respond with zero wait states.

7-15