BEO

BEl

BE2

BE3

BEO

BEl

BE2

BE3

BEO

LOCAL

BUS

INTERFACE

BYTE

ADDRESS

0

1

2

3

4

5

6

7

8

-

-

-

WORD

ADDRESS

0

0

2

2

4

4

6

6

8

-

-

-

131

24123 16115

81

7

BE3#

BE2# BE1#

DWORD

ADDRESS

0

0

0

0

4

4

4

4

8

-

-

-

BEO#

01

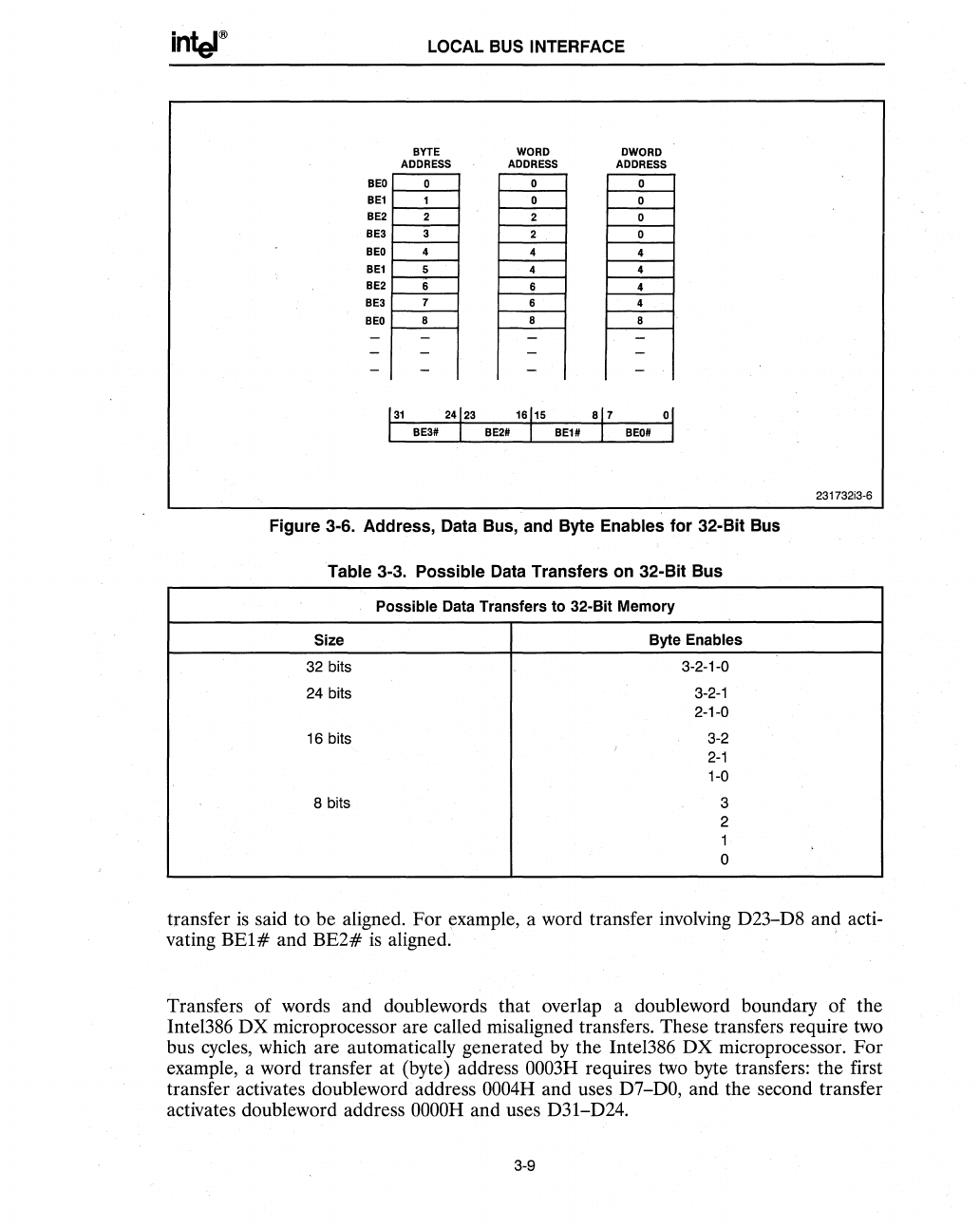

Figure 3-6. Address, Data Bus, and Byte Enables for 32-Bit Bus

Table 3-3. Possible Data Transfers on 32-Bit Bus

Possible

Data Transfers

to

32-Bit

Memory

Size

Byte Enables

32 bits

3-2-1-0

24 bits

3-2-1

2-1-0

16 bits

3-2

2-1

1-0

8 bits

3

2

1

0

231732i3-6

transfer

is

said to be aligned. For example, a word transfer involving D23-D8 and acti-

vating

BEl

# and

BE2#

is

aligned.

Transfers of words and doublewords that overlap a doubleword boundary of the

Intel386

DX

microprocessor are called misaligned transfers. These transfers require two

bus cycles, which are automatically generated

by

the Intel386

DX

microprocessor.

For

example, a word transfer at (byte) address 0003R requires two byte transfers: the first

transfer activates doubleword address

0004R and uses D7-DO, and the second transfer

activates doubleword address

OOOOR

and uses D3l-D24.

3-9