TEST CAPABILITIES

TOEAX

231732i12-1

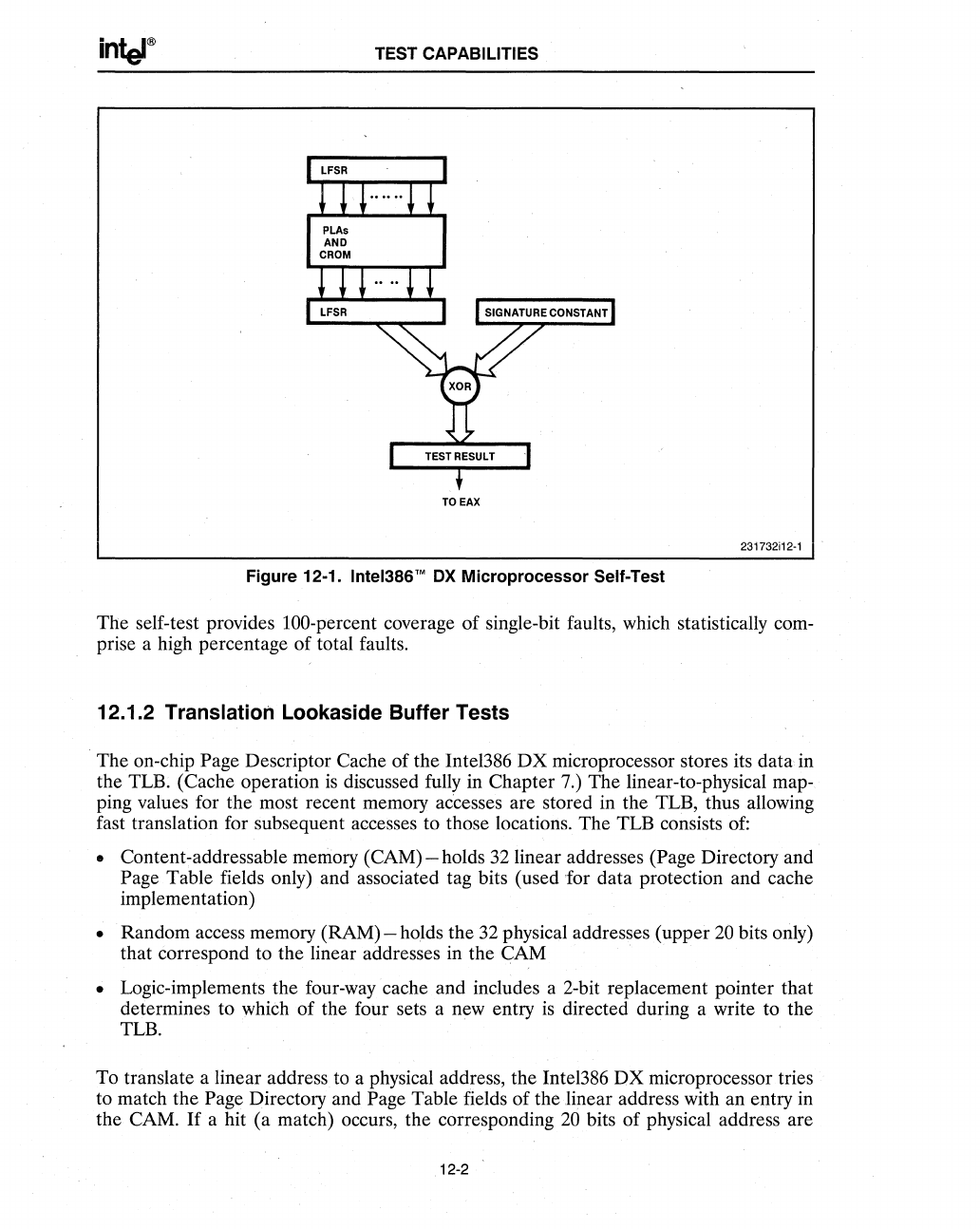

Figure 12-1. Intel386™

OX

Microprocessor Self-Test

The self-test provides lOO-percent coverage of single-bit faults, which statistically com-

prise a high percentage of total faults.

12.1.2 Translation Lookaside Buffer Tests

The on-chip Page Descriptor Cache of the Inte1386 DX microprocessor stores its data in

the

TLR

(Cache operation

is

discussed fully in Chapter 7.) The linear-to-physical

map-.

ping values for the most recent memory accesses are stored in the TLB, thus allowing

fast translation for subsequent accesses to those locations_ The TLB consists

of:

• Content-addressable memory

(CAM)-holds

32

linear addresses (Page Directory and

Page Table fields only) and associated tag bits (used for data protection and cache

implementation)

• Random access memory (RAM) - holds the

32

physical addresses (upper

20

bits only)

that correspond to the linear addresses in the CAM

• Logic-implements the four-way cache and includes a 2-bit replacement pointer that

determines to which of the four sets a new entry

is

directed during a write to the

TLR

To translate a linear address to a physical address, the Intel386

OX

microprocessor tries

to match the

Page Directory and Page Table fields of the linear address with an entry in

the CAM.

If

a hit

(a

match) occurs, the corresponding

20

bits of physical address are

12-2