CLK2

CLK

BEO#-BE3#,

A2-A31,

MIIO#, D/C#

WIR#

AOS#

BS16#

IDLE

I

CVCLE1

NON·PIPELINED

(WRITE)

TI

T1

T2

~JVq

~£.lllp~

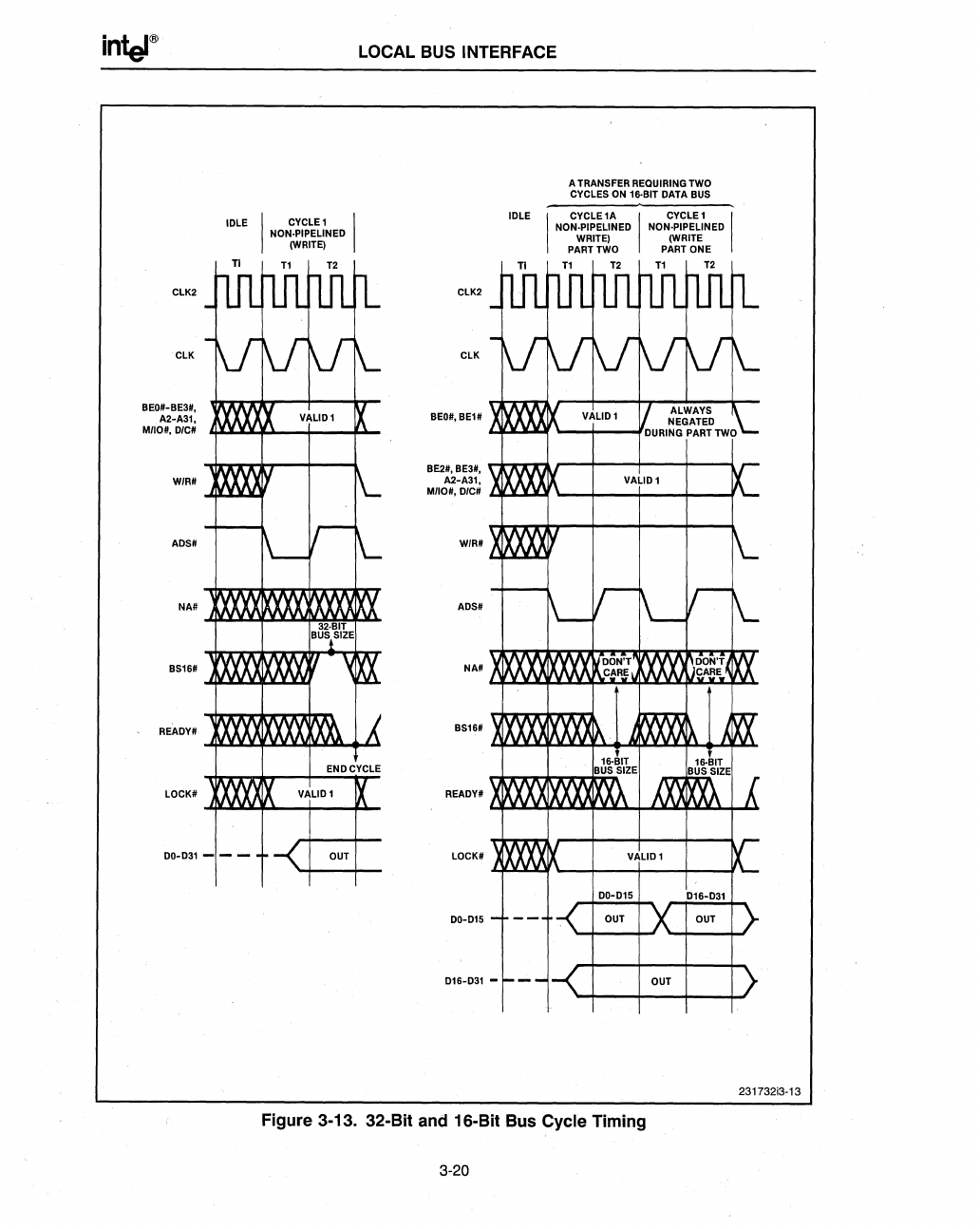

LOCAL BUS INTERFACE

CLK2

CLK

BEO#,

BE1#

IDLE

TI

A TRANSFER REQUIRING TWO

CYCLES ON 16·BIT

DATA BUS

CVCLE1A

NON·PIPELINEO

WRITE)

PART TWO

T1

T2

CVCLE1 I

NON·PIPELINED

(WRITE

PART

ONE

T1

T2

CJpL.l£lUt"'----I-~

BE2#, BE3#,

nb~-,j,V"--i---i---i--""i

A2-A31 ,

MIIO#, OIC#

.ajC:J.~I£lI'\.--+---+---+---f

AOS#

B516#

00-015

Figure 3-13. 32-Bit and 16-Bit

Bus

Cycle Timing

3-20

231732i3-13