CACHE SUBSYSTEMS

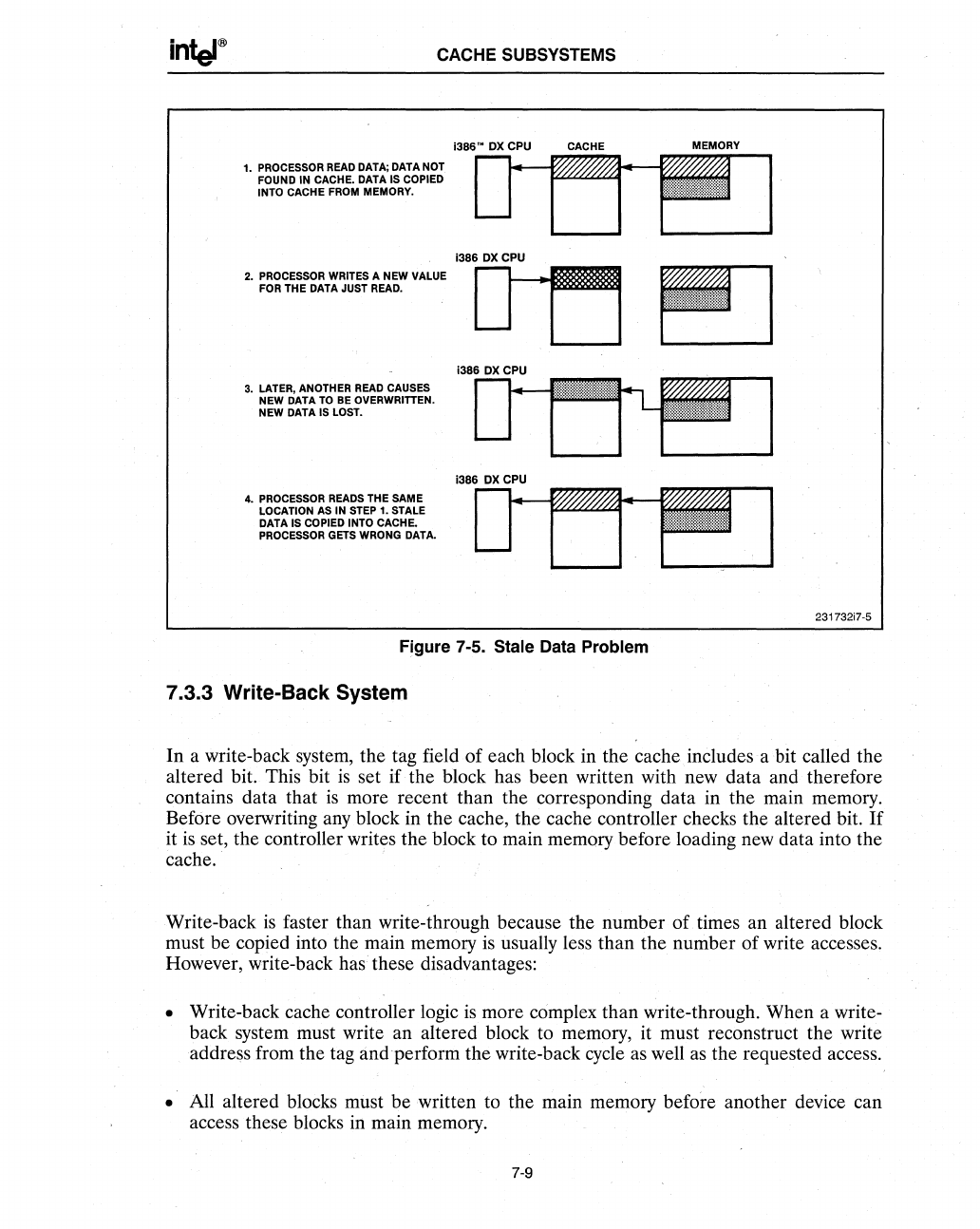

1.

PROCESSOR READ DATA; DATA NOT

FOUND IN

CACHE. DATA IS COPIED

INTO

CACHE FROM MEMORY.

2.

PROCESSOR WRITES A NEW VALUE

FOR

THE DATA JUST READ.

3.

LATER, ANOTHER READ CAUSES

NEW DATA

TO

BE

OVERWRITTEN.

NEW DATA IS LOST.

4. PROCESSOR READS THE SAME

LOCATION AS IN STEP 1. STALE

DATA

IS COPIED INTO CACHE.

PROCESSOR GETS WRONG DATA.

;3B6

OX

CPU

o-u

Figure 7-5. Stale Data Problem

7.3.3 Write-Back System

231732;7·5

In

a write-back system, the tag field

of

each block in the cache includes a bit called the

altered bit. This bit

is

set if the block has been written with new data and therefore

contains data that

is

more recent than the corresponding data in the main memory.

Before overwriting any block in the cache, the cache controller checks the altered bit.

If

it

is

set, the controller writes the block to main memory before loading new data into the

cache.

Write-back

is

faster than write-through because the number

of

times an altered block

must be copied into the main memory

is

usually less than the number

of

write accesses.

However, write-back has these disadvantages:

• Write-back cache controller logic

is

more complex than write-through. When a write-

back system must write an altered block to memory, it must reconstruct the write

address from the tag and perform the write-back cycle as well

as

the requested access.

• All altered blocks must be written to the main memory before another device can

access these blocks in main memory.

7-9