Figure

7-15

7-16

8-1

8-2

8-3

8-4

8-5

8-6

8-7

8-8

8-9'

8-10

8-11

8-12

8-13

8-14

8-15

8-16

8-17

9-1

9-2

9-3

9-4

9-5

9-6

9-7

9-8

9-9

9-10

9-11

9-12

10-1

10-2

11-1

11-2

11-3

11-4

11-5

11-6

11-7

11-8

11-9

11-10

11-11

11-12

11-13

11-14

11-15

11-16

11-17

11-18

11-19

11-20

11-21

11-22

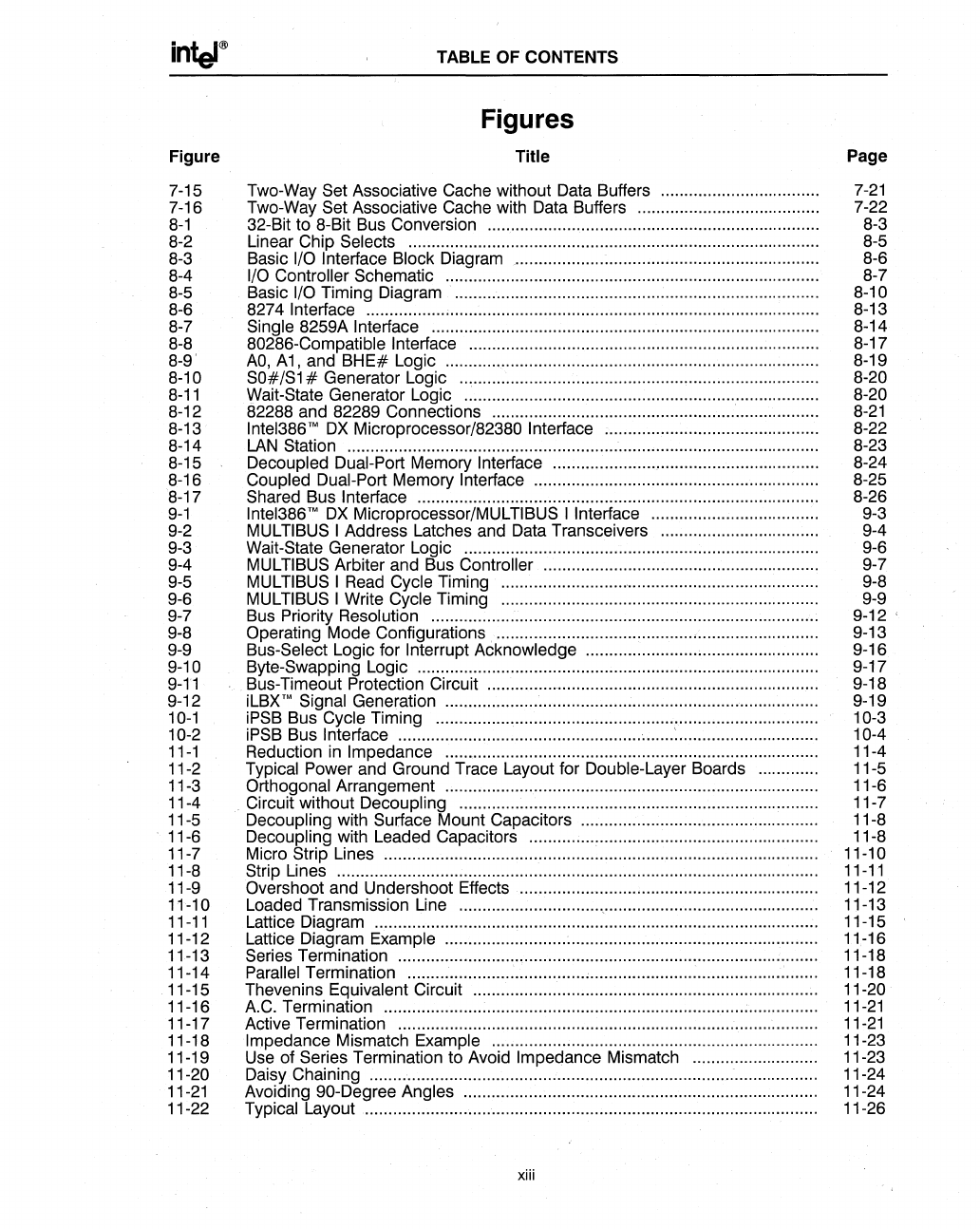

TABLE OF CONTENTS

Figures

Title

Two-Way

Set

Associative

Cache

without

Data

Buffers

................................. .

Two-Way

Set

Associative

Cache

with

Data

Buffers

...................................... .

32-Bit

to

8-Bit

Bus

Conversion

...................................................................... .

Linear

Chip

Selects

....................................................................................... .

Basic

I/O

Interface

Block

Diagram

, .................. : ............................................ .

I/O

Controller

Schematic

............................................................................... .

Basic

I/O

Timing

Diagram

............................................................................. .

8274

Interface

................. ; .............................................................................. .

Single

8259A

Interface

.................................................................................. .

80286-Compatible

Interface

.......................................................................... .

AO,

A1,

and

BHE#

Logic

............................................................................... .

SO#/S1

#

Generator

Logic

............................................................................. .

Wait-State

Generator

Logic

........................................................................... .

82288

and

82289

Connections

..................................................................... .

Intel386™

DX

Microprocessor/82380

Interface

............................................. .

LAN

Station

.................................................................................................... .

Decoupled

Dual-Port

Memory

Interface

........................................................ .

Coupled

Dual-Port

Memory

Interface

............................................................ .

Shared

Bus

Interface

..................................................................................... .

Intel386™

DX

Microprocessor/MUL

TIBUS

I

Interface

................................... .

MUL

TIBUS

I

Address

Latches

and

Data

Transceivers

................................. .

Wait-State

Generator

Logic

........................................................................... .

MUL

TIBUS

Arbiter

and

Bus

Controller

.......................................................... .

MUL

TIBUS

I

Read

Cycle

Timing

........................... ' ........................................ .

MULTIBUS

I

Write

Cycle

Timing

................................................................... .

Bus

Priority

Resolution

.................................................................................. .

Operating

Mode

Configurations

.......................................... , ......................... .

Bus-Select

Logic

for

Interrupt

Acknowledge

........................ ; ........................ .

Byte-Swapping

Logic

..................................................................................... .

Bus-Timeout

Protection

Circuit

...................................................................... .

iLBXTM

Signal

Generation

................................................................................ .

iPSB

Bus

Cycle

Timing

................ , ................................................................ .

iPSB

Bus

Interface

............................................................

~

............................. .

Reduction

in

Impedance

................................................................................ .

Typical

Power

and

Ground

Trace

Layout

for

Double-Layer

Boards

............ .

Orthogonal

Arrangement

............................................................................... .

.

Circuit

without

Decoupling

.................................................................... , ....... .

Decoupling

with

Surface

Mount

Capacitors

.................................................. .

Decoupling

with

Leaded

Capacitors

.......... ;

...

, .............................................. .

Micro

Strip

Lines

............................................................................................ .

Strip

Lines

...................................................................................................... .

Overshoot

and

Undershoot

Effects

............................................................... .

Loaded

Transmission

Line

............................... , ............................................. .

Lattice

Diagram

.............................. , ............................................................... .

Latt.ice

Diag~am.Example

..........................

~

.................................................... .

Senes

Termination

......................................................................................... .

Parallel

Termination

....................... ' ............... ; ......................................... : ...... .

Thevenins

Equivalent

Circuit

......................................................................... .

A.C.

Termination

............................................................................. ; .............. .

Active

Termination

......................................................................................... .

Impedance

Mismatch

Example

..................................................................... .

Use

of

Series

Termination

to

Avoid

Impedance

Mismatch

.......................... .

Daisy

Chaining

................................................................................................ .

Avoiding

90-Degree

Angles

........................................................................... .

Typical

Layout

' ................................................................................................ .

xiii

Page

7-21

7-22

8-3

8-5

8-6

8-7

8-10

8-13

8-14

8-17

8-19

8-20

8-20

8-21

8-22

8-23

8-24

8-25

8-26

9-3

9-4

9-6

9-7

9-8

9-9

9-12

'

9-13

9-16

9-17

9-18

9-19

10-3

10-4

11-4

11-5

11-6

11-7

11-8

11-8

11-10

11-11

11-12

11-13

11-15

11-16

11-18

11-18

11-20

11-21

11-21

11-23

11-23

11-24

11-24

11-26