LOCAL BUS INTERFACE

32

DATA

BUS

(00-031)

1386'·

OX

32-BIT

CPU

ADDRESS

BUS

(BEO#-BE3#.A2-A31)

I.lEI.lORY

TBS16#

"HIGH"

32

DATA

BUS

(00-D31)

ADDRESS

BUS

(BEO#-BE3#,

A2-A31)

16

DATA

BUS

(00-DI5)

231732;3-14

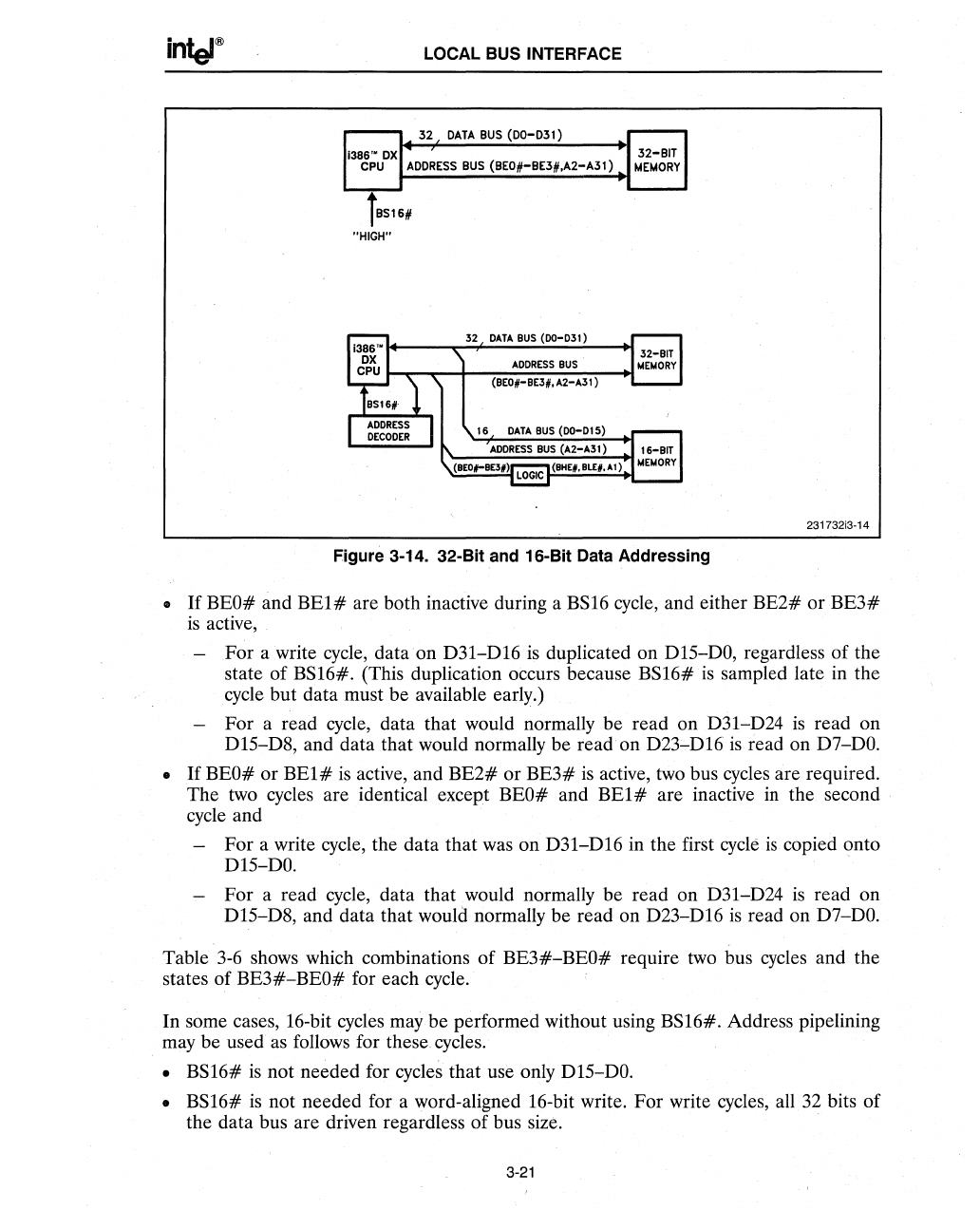

Figure 3-14. 32-Bit

.and

16-Bit Data Addressing

•

If

BEO# and

BEI#

are both inactive during a BSl6 cycle, and either

BE2#

or

BE3#

is

active,

For a write

cycle,

data on

D31-D16is

duplicated on DIS-DO, regardless of the

state of BSI6#. (This duplication occurs because

BSI6#

is

sampled late in the

cycle

but data must be available early.)

For a read cycle, data that would normally be read on D31-D24

is

read on

DIS-D8, and data that would normally be read on

D2J-DI6

is

read on D7-DO.

•

If

BEO# or

BEl

#

is

active, and

BE2#

or

BE3#

is

active,

two

bus cycles are required_

The two cycles are identical except

BEO# and

BEl

# are inactive

in

the second

cycle

and

For a write cycle, the data that

was

on D31-D16 in the first

cycle

is

copied onto

DIS-DO. .

For a read cycle, data that would normally be read on D31-D24

is

read on

DIS-D8, and data that would normally be read on D23-D16

is

read on D7-DO.

Table

3-6

shows which combinations of BE3#-BEO# require two bus

cycles

and the

states of BE3#-BEO# for each cycle.

In some cases, 16-bit cycles

maybe

performed without using BSI6#. Address pipelining

may be used

as

follows for these.

cycles_

•

BSI6#

is

not needed for cycles that use only DIS-DO.

•

BSI6#

is

not needed for a word-aligned 16-bit write. For write cycles, all

32

bits of

the data bus are driven regardless of bus size.

3-21