LOCAL BUS INTERFACE

Table

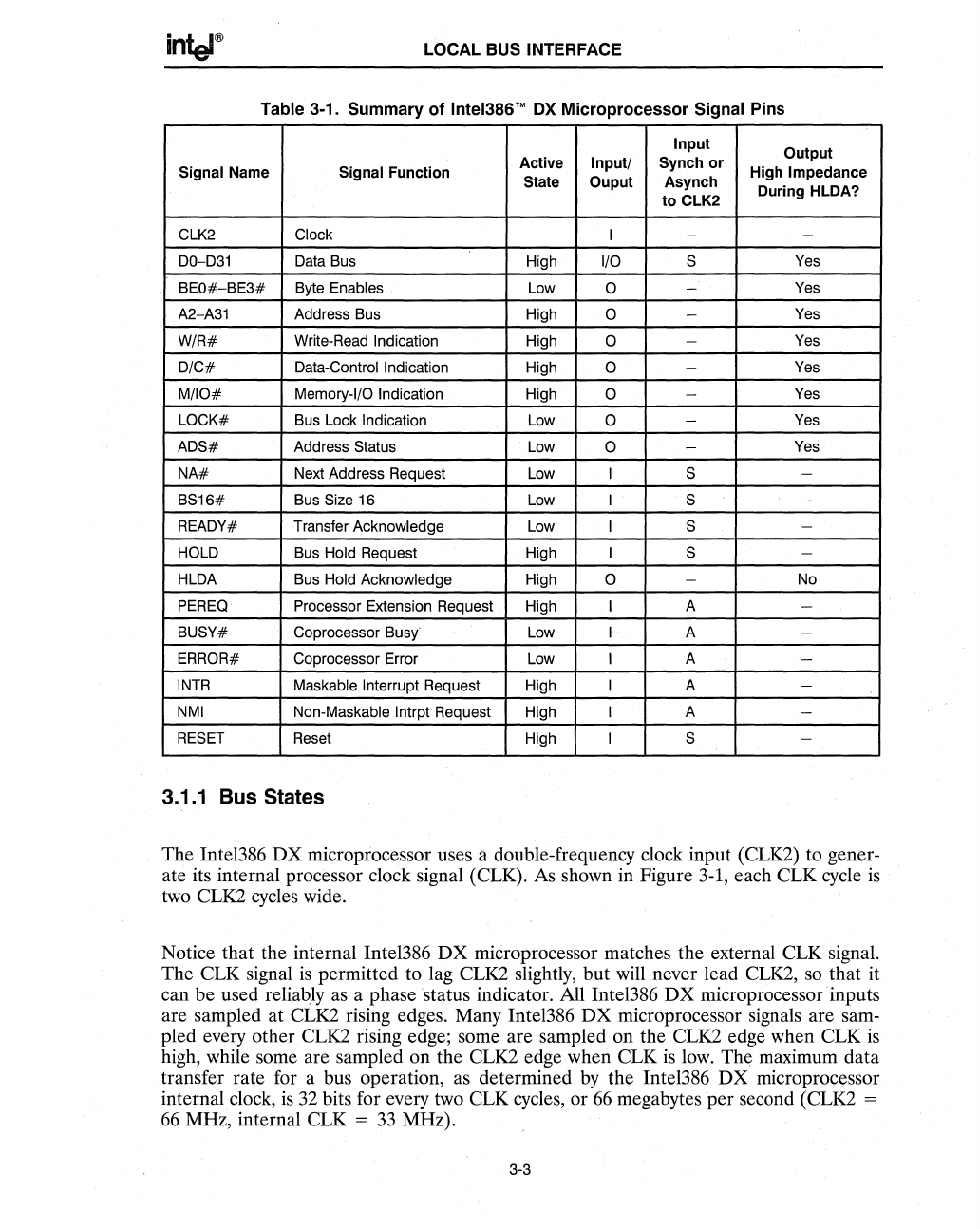

3-1. Summary of Intel386™

OX

Microprocessor Signal Pins

Input

Output

Signal Name Signal Function

Active

Input/

Synch or

High

Impedance

State

Ouput

Asynch

During HLDA?

to CLK2

CLK2

Clock

-

I

- -

DO-D31 Data Bus

High

I/O S

Yes

BEO#-BE3#

Byte Enables

Low

0

- Yes

A2-A31

Address Bus High

0

-

Yes

W/R#

Write-Read Indication

High 0

- Yes

D/C#

Data-Control Indication

High

0

- Yes

M/IO#

Memory-I/O Indication High

0

- Yes

LOCK# Bus Lock Indication Low

0

-

Yes

ADS#

Address Status Low

0

- Yes

NA#

Next Address Request Low I S

-

BS16#

Bus Size 16 Low I S

-

READY#

Transfer

Acknowledge Low I S

-

HOLD

Bus Hold Request High I S

-

HLDA Bus Hold Acknowledge High

0

-

No

PEREQ Processor Extension

Request

High I

A

-

BUSY#

Coprocessor Busy·

Low I A

-

ERROR# Coprocessor Error Low I A

-

INTR Maskable Interrupt Request High

I

A

-

NMI Non-Maskable Intrpt Request

High

I

A

-

RESET

Reset High

I S

-

3.1.1

Bus

States

The Intel386 DX microprocessor uses a double-frequency clock input (CLK2) to gener-

ate its internal processor clock signal (CLK).

As

shown in Figure

3-1,

each CLK cycle

is

two CLK2 cycles wide.

Notice

that· the internal Inte1386

DX

mieroprocessor matches the external CLK signal.

The CLK signal

is

permitted to lag CLK2 slightly, but will never lead

CLK2,

so that it

can be used

relia~ly

as

a phase status indicator. All Inte1386 DX microprocessor inputs

are sampled at CLK2 rising edges. Many Inte1386

DX

microprocessor signals are sam-

pled every other CLK2 rising edge; some are sampled on the CLK2 edge when CLK

is

high, while some are sampled on the CLK2 edge when CLK

is

low.

The maximum data

transfer rate for a bus operation, as determined

by

the Intel386 DX microprocessor

internal clock,

is

32

bits for every two CLK cycles,or

66

megabytes per second (CLK2 =

66

MHz, internal CLK =

33

MHz).

3-3