PHYSICAL DESIGN AND DEBUGGING

PAGE

66,132

EQUATES

,

LATCH

EQU

0C8H

;PRESUMES

A

HARDWARE

;LATCH

IS

AT

I/O

ADDR

C8H

GOOD-SIGNAL

EQU

0AAH

BAD-SIGNAL

EQU

055H

CODE

TO

VERIFY

ABILITY

TO

WRITE

AND

READ

RAM

CORRECTLY

ASSUME

CS:INITIAL_CODE

INITIAL_CODE

SEGMENT

ORG

0F000H

;THIS

IS

INTENDED

TO

BE

LOCATED

;AT

PHYSICAL

ADDRESS

FFFFF000H

TSLLOOP:

MOV

BX,

0000H

;INITIALIZE

BASE

~EGISTER

TO

0

MOV

DS,

BX

;INITIALIZE

DS

REGISTER

TO

0

MOV

rBX],

5473H

;WRITE

5473H

TO

RAM

ADDR

0

AND

1

MOV

rBX]+2,

2961H

lWRITE

2961H

TO

RAM

ADDR

2

AND

3

JMP

READ

lJMP

TO

FORCE

CPU

TO

BREAK

lPRE-FETCH

QUEUE

AND

FETCH

THE

lNEXT

INSTRUCTION

AGAIN.

THIS

lPREVENTS

THE

RAM

DATA

WRITTEN

lFROM

JUST

LINGERING

ON

THE

DATA

lBUS

UNTIL

THE

READ

OCCURS

READ:

CMP

rBX],

5473H

lREAD

DATA

FROM

RAM

AD

DR

0

AND

1

;AND

COMPARE

WITH

VALUE

WRITTEN

JNE

BADRAM

;IF

DATA

DOESN'T

MATCH,

THEN

JMP

CMP

rBX]+2,

2961H

lREAD

DATA

FROM

RAM

ADDR

2

AND

3

lAND

COMPARE

WITH

VALUE

WRITTEN

JNE

BADRAM

;IF

DATA

DOESN'T

MATCH,

THEN

JMP

MOV

.AL,

GOOD-SIGNAL

OUT

LATCH,

AL

lSIGNAL

THAT

DATA

WAS

CORRECT

JMP

TSLLOOP

BADRAM:

MOV

AL,

BAD-SIGNAL

OUT

LATCH,

AL

lSIGNAL

THAT

DATA

WAS

BAD

JMP

TSLLOOP

ORG

0FFF0H

lPOSITION

THE

FOLLOWING

INSTRUCTION

lAT

OFFSET

0FFF0H

START:

JMP

TST-LOOP

lINTRA-SEGMENT

JUMP

(WITHIN

l

SEGMENT)

lTHIS

IS

INTENDED

TO

BE

THE

FIRST

lINSTRUCTION

EXECUTED,

SO

IT

MUST

lBE

LOCATED

AT

PHYSICAL

ADDRESS

lFFFFFFF0H.

INITIAL_CODE

ENDS

END

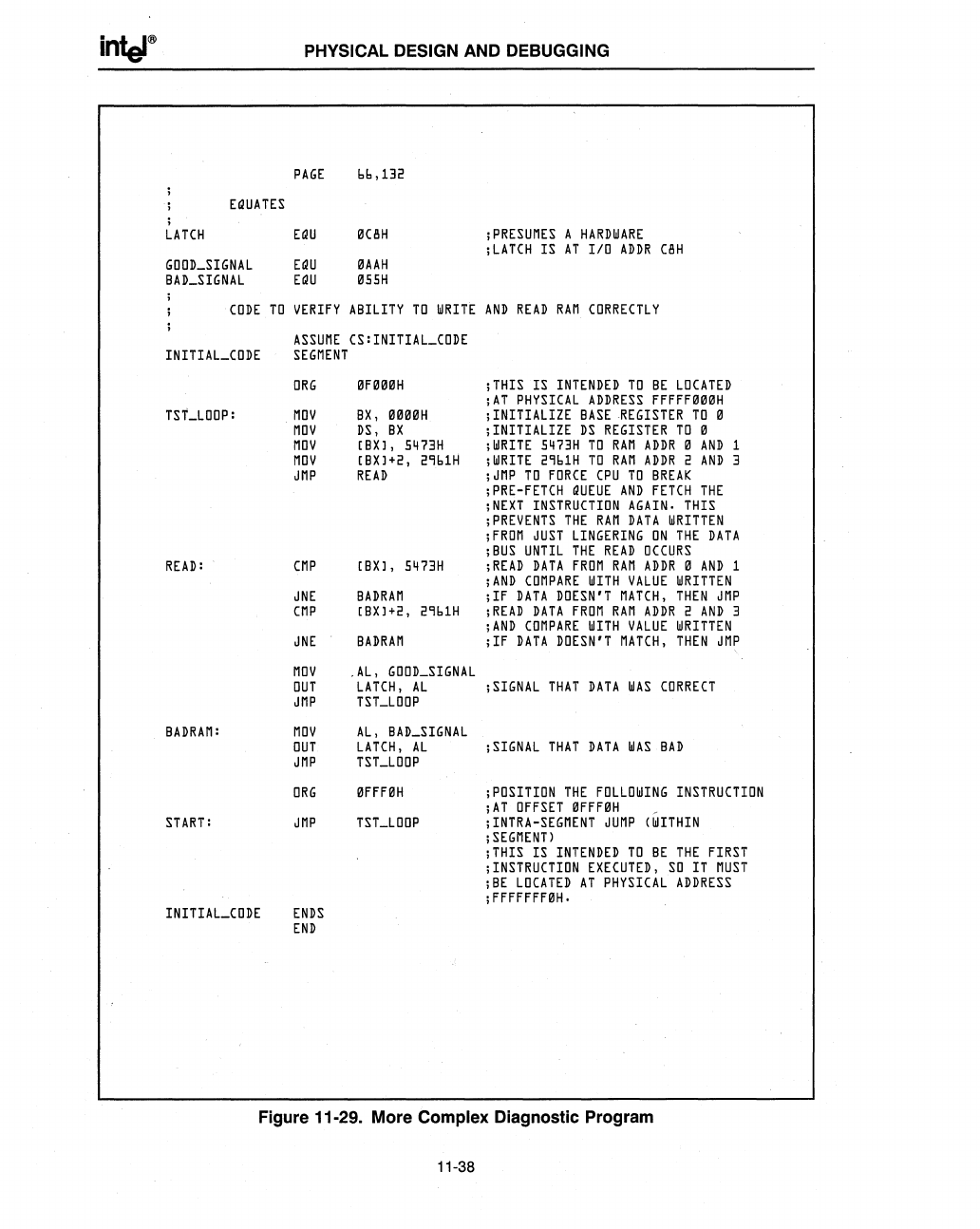

Figure 11-29. More Complex Diagnostic Program

11-38