I/O INTERFACING

...

II

BYTE

ENABLES

)

Ao/A1

...

".

LOGIC

ADDRESS

LATCHED

ADDRESS

LATCH

1386

DX

CPU

ADDRESS

-

~

'"

ADDRESS

~

....

DECODER

1386'· DX

".

CPU

.A

.A

DATA

1386 DX CPU DATA

TRANSCEIVER

DATA

'f

'"

'f

....

80386

STATUS

50#/51#

r-

LOGIC

".

~

82288

BUS

CONTROLLER

,

WAIT-5TATE

GENERATOR

......

J

82289

~

BUS

ARBITER

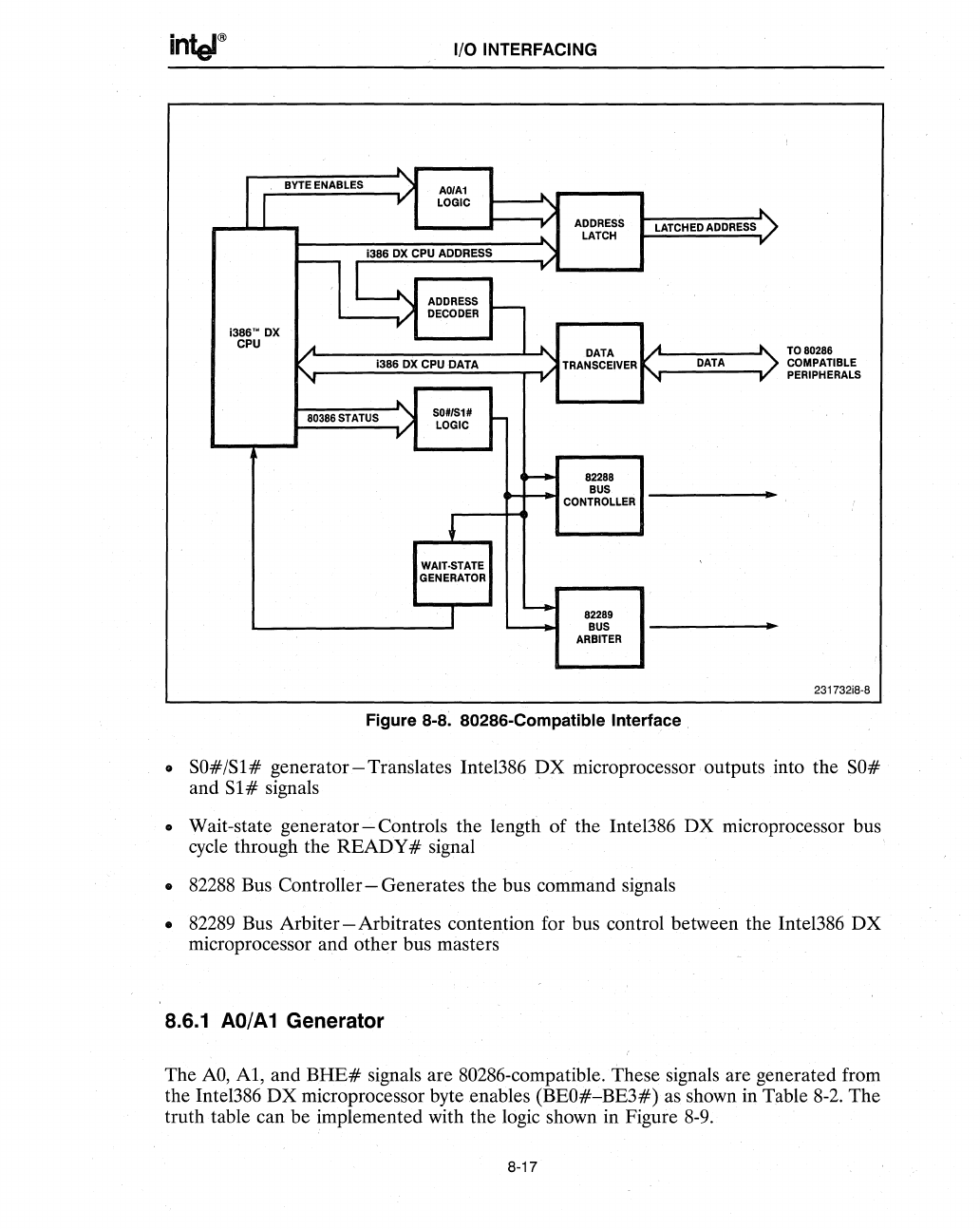

Figure

8-8~

80286-Compatible Interface.

....

'"

...

".

..

..

TO

80286

COMPATIBLE

PERIPHERALS

231732i8-8

• SO#/Sl# generator-Translates Intel386 DX microprocessor outputs into the

SO#

and

Sl

# signals .

•

Wait-state generator-Controls the length of the Intel386 DX microprocessor bus

cycle

through the

READY#

signal

•

82288

Bus Controller - Generates the bus command signals

•

82289

Bus

Arbiter-Arbitrates

contention for bus control between the Intel386

DX

microprocessor and other bus masters

8.6.1

AO/

A 1 Generator

The

AO,

A1, and

BHE#

signals are 80286-compatible. These signals are generated from

the

Inte1386

DX microprocessor byte enables (BEO#-BE3#)

as

shown in Table

8-2.

The

truth table can be implemented with the logic shown in Figure

8-9.

8-17