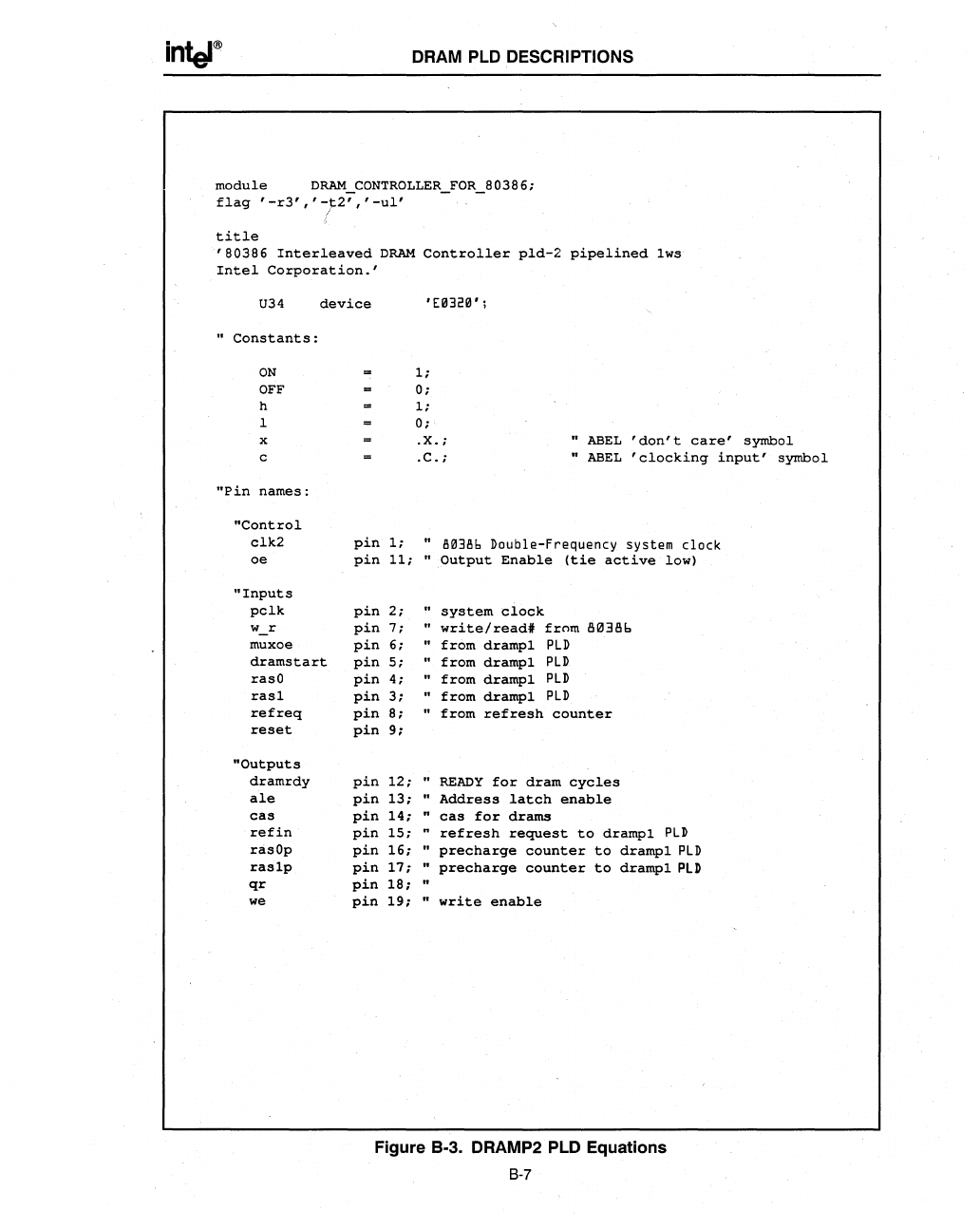

DRAM

PLD

DESCRIPTIONS

module

flag

'-r3'

1'~~2'

,'-ul'

title

'80386

Interleaved

DRAM

Controller

pld-2

pipelined

1ws

Intel

Corporation.'

U34

device

'E~32~';

"

Constants:

ON

OFF

h

1

x

c

"Pin

names:

"Control

clk2

oe

"Inputs

pclk

w r

muxoe

dramstart

rasO

ras1

refreq

reset

"Outputs

dramrdy

ale

cas

refin

rasOp

ras1p

qr

we

1;

0;

1;

0;

.x.

;

.C.

;

" ABEL

'don't

care'

symbol

"

ABEL

'clocking

input'

symbol

pin

1;

"80386

Double-Frequency system

clock

pin

11;

"

Output

Enable

(tie

active

low)

pin

2;

pin

7;

pin

6;

pin

5;

pin

4;

pin

3;

pin

8;

pin

9;

"

system

clock

..

write/readit

from

8111386

"

from

dramp1

PLD

"

from

dramp1

PLD.

"

from

drampl

PLD

"

from

dramp1

PLD

"

from

refresh

counter

pin

12;

" READY

for

dram

cycles

pin

13;

"

Address

latch

enable

pin

14;

n

cas

for

drams

pin

15;

n

refresh

request

to

dramp1

PLD

pin

16;

"

precharge

counter

to

dramp1

PLD

pin

17;

"

precharge

counter

to

dramp1

PLD

pin

18;

"

pin

19;

"

write

enable

Figure 8-3. DRAMP2

PLD

Equations

S·7