ClK2 [

ClK [

BEl

#.

BE2#.

BE3#

[

BEO#.

A3-A31. [

M/IO#.

D/C#.

W/R#

lOCK# [

ADS#

[

00-07

[

08-031

[

LOCAL BUS INTERFACE

PREVIOUS

I

CYCLE

T2

T1

INTERRUPT

ACKNOWLEDGE

CYCLE

I

T2

T2

TI

JUl

rut rut

rul

rut

-V

V V

V V

....

~

,Jf\Jf\

...

"'V'ir"

",...&....,

.1'1.

.1'1.

--

'"-,

X X X

X X

: X

IGNORED

X

X X

:XY

w...

~X

IGNORED

.

----

---- -----

--0--

IGNORED

.

----

..

---

-----

--cp--

IDLE

(4

BUS

STATES)

TI

Ti

rut rut

V V

,Jf\X

XX

,X

,X

X X

.X X

XX

X

----

-----

----

-----

ACKNOWLEDGE

CYCLE

2

IOLE

I

INTERRUPT

Tl

11

T2

T21

n

ill

h.Il

rut

rul

n.n.

V V

V

V V

X

XX

r

.Jf\Jf\

lXX)!

XXX)!

/"

X

~XX

XX

,/

.(OJ.

,"-V

X X

.X

X X

,<IGNORED

XXX)!

:X

X Y

w...

m

VECTOR

.....

--

-----

----

--0---

IGNORED

-----

..........

----

--cp---

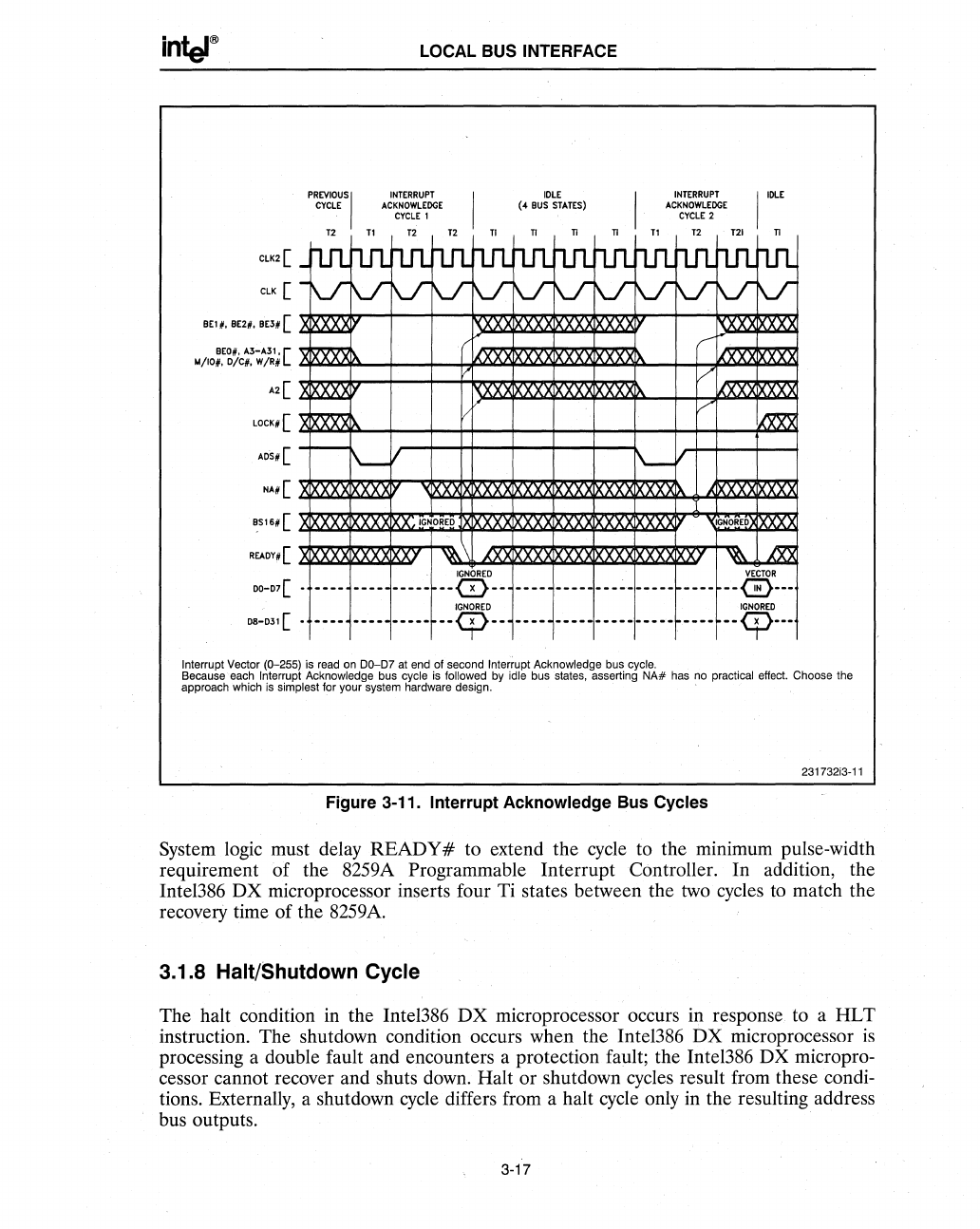

Interrupt Vector (0-255) is read on DO-D7 at end of second Interrupt Acknowledge bus cycle.

Because each

Interrupt Acknowledge bus cycle

is

followed by idle bus states. asserting

NA#

has no practical effect. Choose the

approach which is simplest for your system hardware design.

231732i3-11

Figure 3-11. I nterrupt Acknowledge Bus Cycles

System logic must delay

READY

# to extend the cycle to the minimum pulse-width

requirement of the 8259A Programmable Interrupt Controller. In addition, the

Intel386

DX

microprocessor inserts four Ti states between the two cycles to match the

recovery time of the 8259A.

3.1.8 Halt/Shutdown Cycle

The halt condition in the Intel386

DX

microprocessor occurs in response to a

HLT

instruction. The shutdown condition occurs when the Inte1386

DX

microprocessor

is

processing a double fault and encounters a protection fault; the Intel386 DX micropro-

cessor cannot recover and shuts down. Halt

or

shutdown cycles result from these condi-

tions. Externally, a shutdown

cycle

differs from a halt cycle only in the resulting address

bus outputs.

3·17