I/O INTERFACING

MIlO.

-

.....

+-HI-.:I~

....

DIC.

--t-;~=r-\---+---.J

WIR.

CHIP

SELECT

------4~

__

,

FOR

B0286

COMPATIBLES

WS1

----------~r_~

WS2

-----------..,'-~

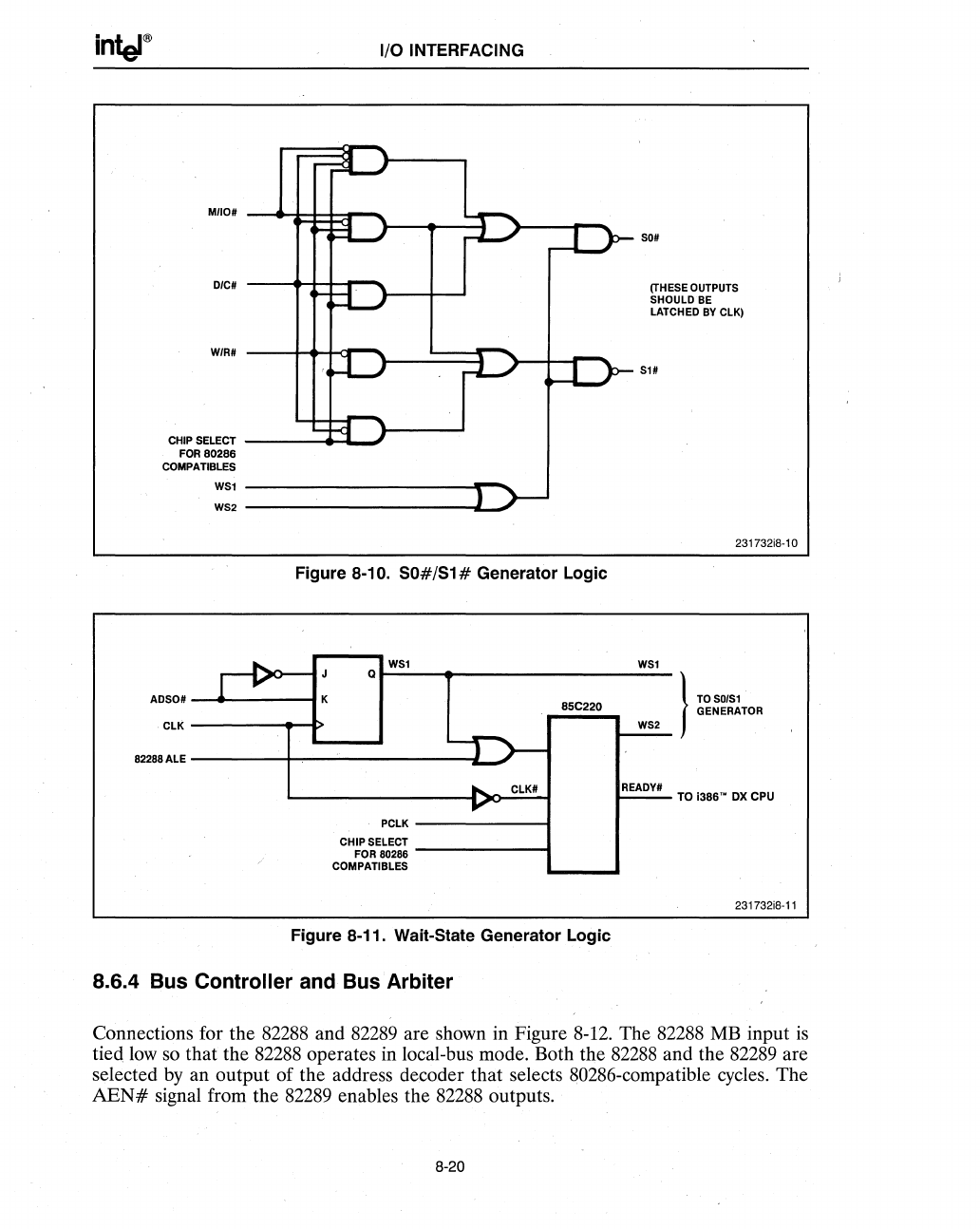

Figure 8-10.

SO#/S1#

Generator Logic

r1>

WS1

J

Q

K

85C220

AD50.

,

ClK

-

82288 ALE

1

)--

-

......

ClK.

~

PClK

CHIP SELECT

FOR

80286

COMPATIBLES

Figure 8-11. Wait-State Generator Logic

8.6.4 Bus Controller and Bus Arbiter

so.

(THESE

OUTPUTS

SHOULD

BE

lATCHED

BY

ClK)

Sl.

231732i8-10

W51

WS2

I

T050151

GENERATOR

READY#

-

TO

i386'·

OX

CPU

231732i8-11

Connections for the

82288

and

82289

are shown in Figure

8-12.

The

82288

MB

input

is

tied,

low

so that the

82288

operates in local-bus mode. Both the

82288

and the

82289

are

selected

by

an output of the address decoder that selects 80286-compatible cycles. The

AEN#

signal from the

82289

enables the

82288

outputs.

8-20