I/O INTERFACING

Only the dual-ported SRAM

is

shared; the

82586

cannot access the Intel386

DX

miCro-

processor core memory. The

Inte1386

DX

microprocessor and

82586

operate in parallel

except when both require access to the SRAM. In this instance, one processor must wait

while the other completes its access. At all other times, the

two

devices are decoupled.

This interface requires at least one level of data copying to move data between the

Inte1386 DX microprocessor core memory and the

82586

communication channel

mem~

ory.

However, usually the data must be copied to separate the frame header information.

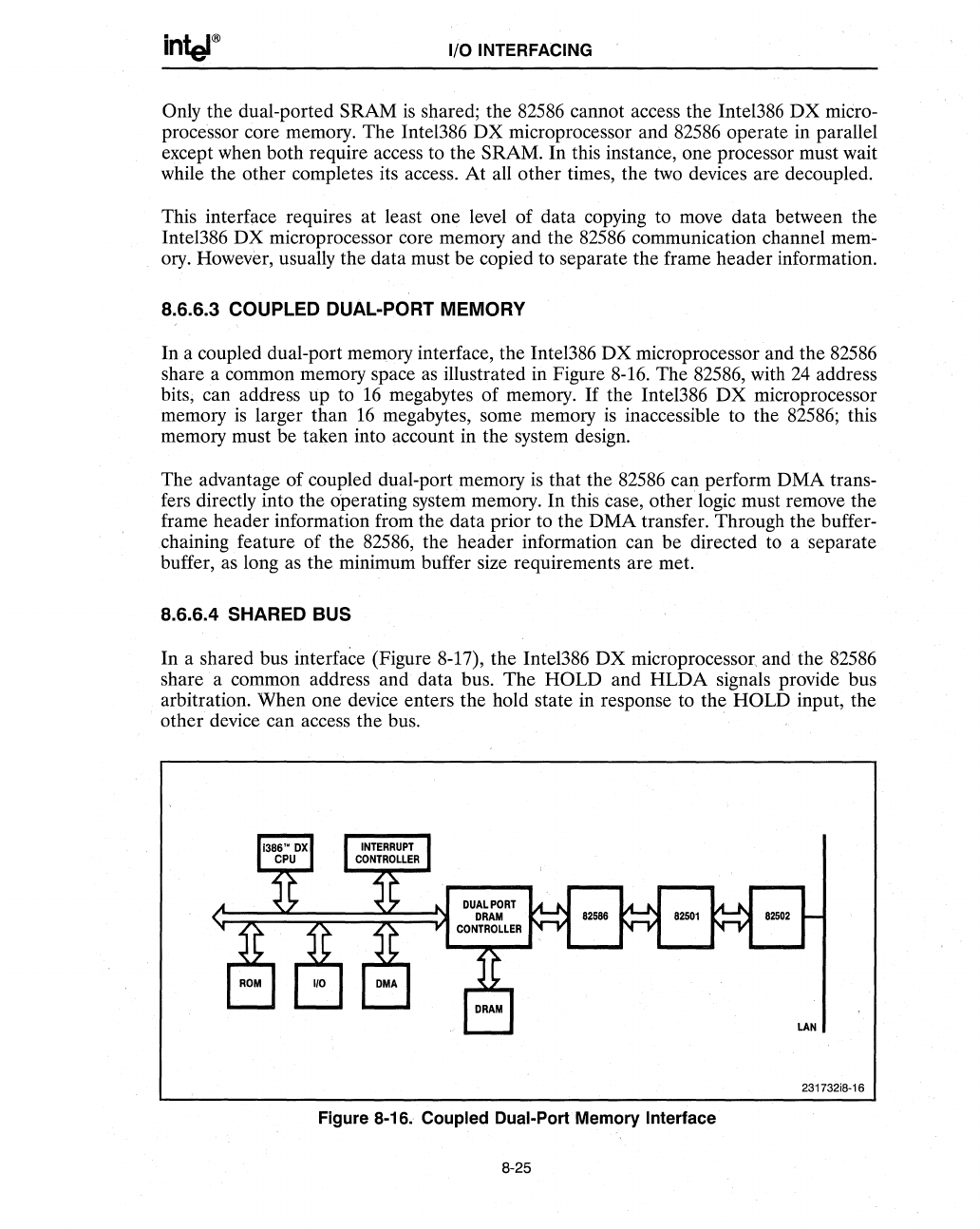

8.6.6.3 COUPLED DUAL-PORT MEMORY

In a coupled dual-port memory interface, the Inte1386 DX microprocessor and the

82586

share a common memory space

as

illustrated in Figure

8-16.

The

82586,

with

24

address

bits; can address up to

16

megabytes of memory.

If

the Inte1386 DX microprocessor

memory

is

larger than

16

megabytes, some memory

is

inaccessible to the

82586;

this

memory must be taken into account in the system design.

The advantage of coupled dual-port memory

is

that the

82586

can perform DMA trans-

fers directly into the operating system memory. In this

case, other logic must remove the

frame header information from the data prior to the DMA transfer. Through the buffer-

chaining feature of the

82586,

the header information can be directed to a separate

buffer,

as

long

as

the minimum buffer size requirements are met.

8.6.6.4 SHARED BUS

In a shared bus interface (Figure 8-17), the Intel386 DX microprocessor and the

82586

share a common address and data bus. The HOLD and HLDA signals provide bus

arbitration. When one device enters the hold state in response to the

HOLD input, the

other device can access the bus.

.

231732i8-16

Figure 8-16. Coupled Dual-Port Memory Interface

8-25