LOCAL BUS CONTROL PLD DESCRIPTIONS

module

clock;

flag

'-r3';

flag

'-ul';

title

'clock

generator

intel

corporation'

"This

85C220

divides

the

doulbe frequency

ClK2

input

"by

two

to

generate

a

single

frequency

ClK.

It

also

"provides

synchronous

reset

outputs

from

an

asynch-

"ronous

reset

input.

The

lowest

two

bits

of

the

DRAM

"refresh

timer

are

included

in

this

PlD.

U2

device

'E0320';

h,l,c,x

=

1,0,

.C.,

.x.;

gnd

pin

10;

vee

pin

20;

o e

pin

11;

clk2

pin

1;

res

pin

2;

refreq

pin

3;

elk

pin

12;

re.elh

pin

13;

re.etl

pin

14;

leO

pin

15;

tel

pin

16;

Icoul

pin

17;

1I0od

pin

18;

re.ync

pin

19;

rt

ImeO

r

II

mel

rllme2

rllme3

•

[ 0 , 0 I

[0,

II

[ 1

,01

[1,

II

"80386

CLK2

"asynchronous

re.et

Input

"low

to

high

Iron.ltlon

requests

refresh

cycle

"low

during

pha.e

1,

high

during

pho.e

2

"high

during

re.et,

changes

during

pha.e

"10.

during

reset,

change.

during

pha.e

1

"bll

0

of

refre.h

timer

"bit

1

of

refresh

Ilmer

"carry

from

bll.

0

and

1

of

refres)

Ilmer

Ill

ow

to

load

refresh

timer

"flip

flop

In

re.el

synchronizer

"elk2

divide

by

Iwo

equation.

elk

:.

!elk;

lire

set

synchronizer

equations

re.yne:·

(res'

!elk>'

(re'ync'

elk);

equations

re.eth

:-

(re.yne

,

!elk)

,

(re.eth

,

elk);

equaiions

re.ell

:.

!re.eth;

"Iowe.t

2

bit.

of

refre.h

timer

.tate_dlagram

[tel,teOI;

state

rtlmeO:

If

(elk)

then

rtlmel

el.e

rtlmeO;

.tote

rtlmel:

If

(elk)

then

rtlme2

else

rtlmel;

.t.te

rtlme2:

If

(elk)

then

rtlme3

else

rtlme2;

• t • t e

,r

tim

e

3:

I f

(e

I

k)

I

hen

r

tim

e 0 e I s e r I I

me

3 ;

"refresh'

Ilmer

e.rry

and

load

.tale_dlagram

[leout,lloadl

.tale

[0,11:

"Idle

If

(tel'

leO'

!refreq

,

!elk)

then

[1,11

el.e

If

(tel'

teO'

refreq"

!elk)

Ihen

[0,01

e I • e

[0,

1 I ;

st.te

[1,11:

"Increment

refre.h

timer

got

0

[0,

1 I ;

.tale

[0,01:

"load

refre.h

timer

go

I 0

[0,

1 I ;

.Iate

[1,01:

"Illegal

got

0

[1,

1 I ;

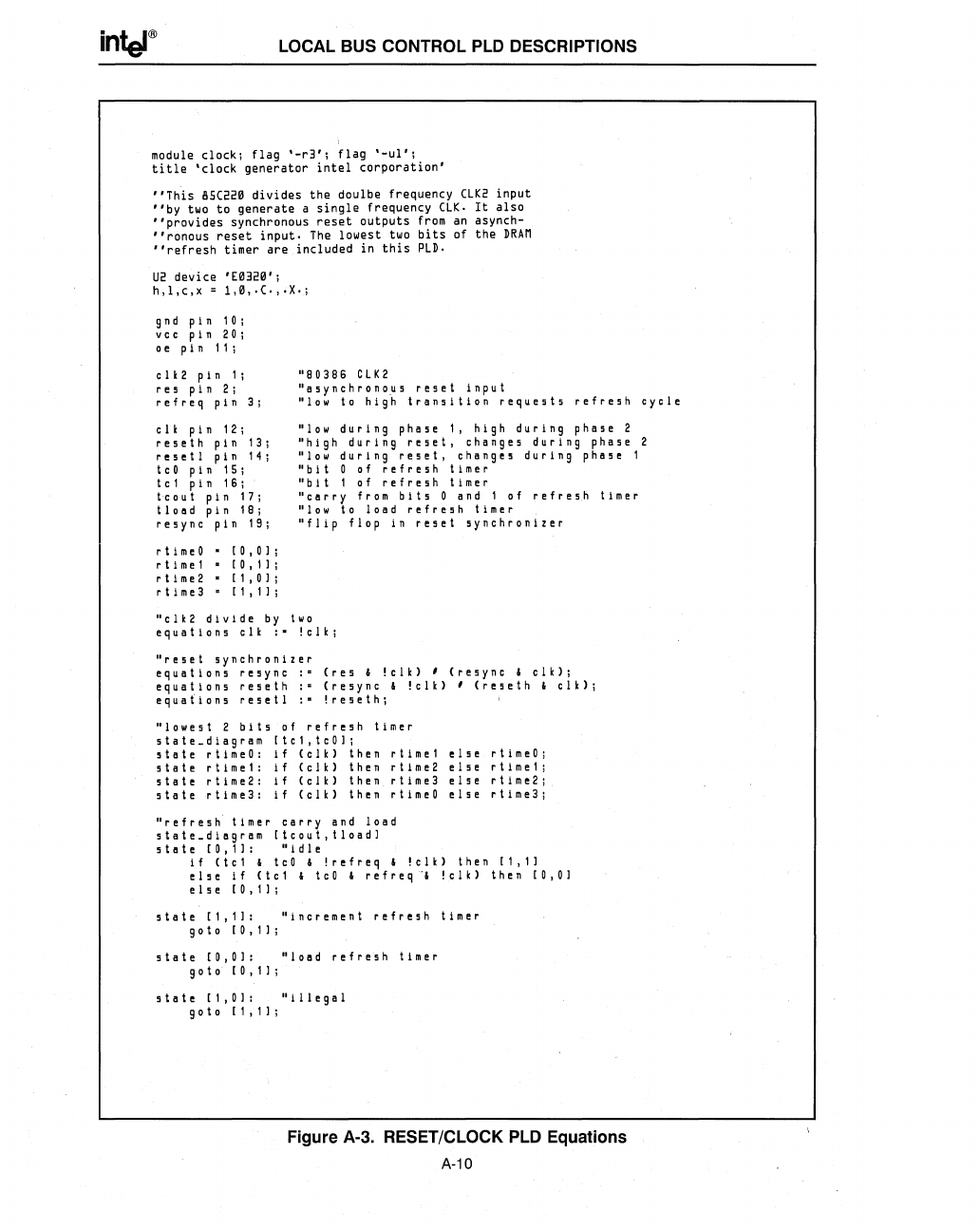

Figure A-3. RESET/CLOCK PLD Equations

A-10