TAG

O

FF

001

~9BITS~

32KS

DATA

24662466

77777777

1+32

BITS--j

RAM

CACHE SUBSYSTEMS

32·BIT

PROCESSOR

ADDRESS

INDEX

I+-

2 x 32K SRAM = 15

BITS--j

1+--16

MEGABYTE DRAM =

24

BITS----.j

DATA INDEX

24862468 7FFC

11223344

7FFB

0010

INDEX

TAG

DATA

OOOC

OOOS

0004

0000

7FFC

001

12345678

7FF8

1FF

11223344

~

0010

-

-

OOOC

-

7FFC

7FFB

0008 000 87654321

P.-

-

12345678

0004

001

11235813

0000

000

13578246

I-

0010

OOOC

1+9BITS~

1+32

BITS--\

OOOS

32KSRAM

-

11235813

0004

77777777 0000

64KCACHE

,,"

l

7FF8

0010

OOOC

87654321

0008

0004

13579246

0000

1+32

BITS--\

16 MEGABYTE DRAM

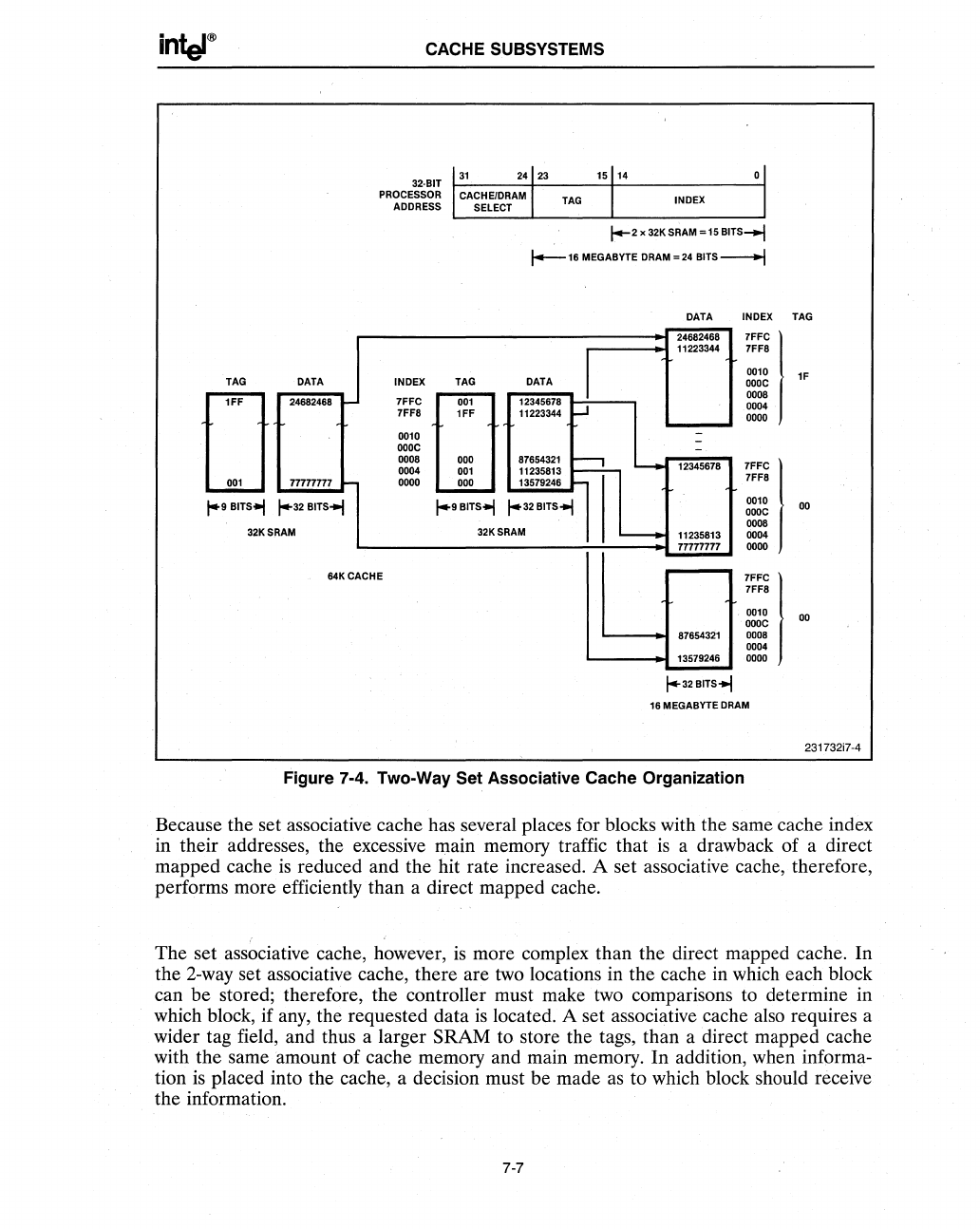

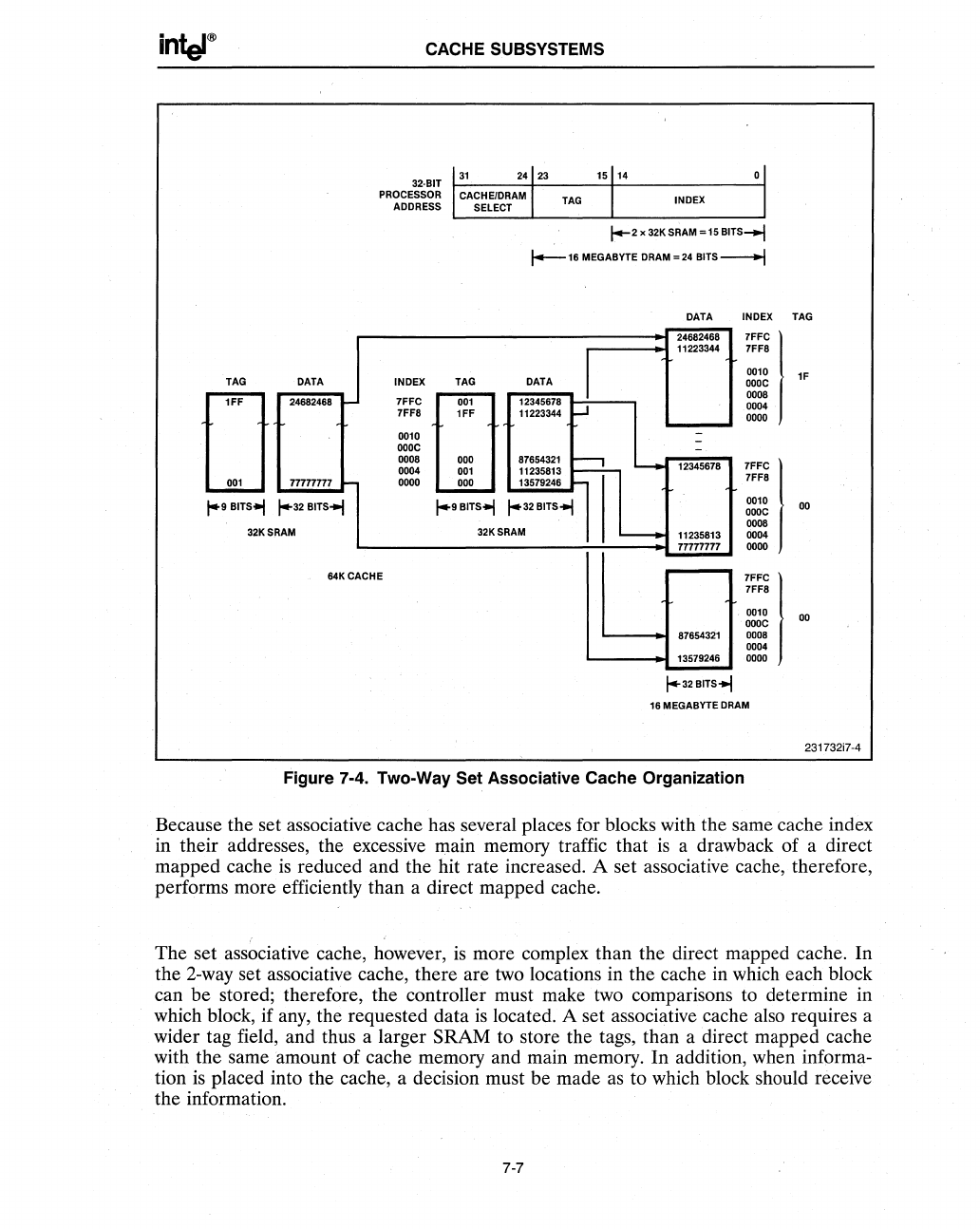

Figure 7-4. Two-Way Set Associative Cache Organization

TAG

IF

00

00

231732;7·4

Because the set associative cache has several places for blocks with the same cache index

in their addresses, the excessive

main memory traffic that

is

a drawback of a direct

mapped cache

is

reduced and the hit rate increased. A set associative cache, therefore,

performs more efficiently than a direct mapped cache.

The set associative cache, however,

is

more complex than the direct mapped cache. In

the

2-way

set associative cache, there are two locations in the cache in which each block

can

be

stored; therefore, the controller must make two comparisons to determine in

which block, if

any,

the requested data

is

located. A set associative cache also requires a

wider tag field, and thus a larger SRAM

to

store the tags, than a direct mapped cache

with the same amount of cache memory and main memory. In addition, when informa-

tion

is

placed into the cache, a decision must be made

as

to which block should receive

the information.

7-7