CHAPTER 2

I NTERNAL ARCHITECTURE

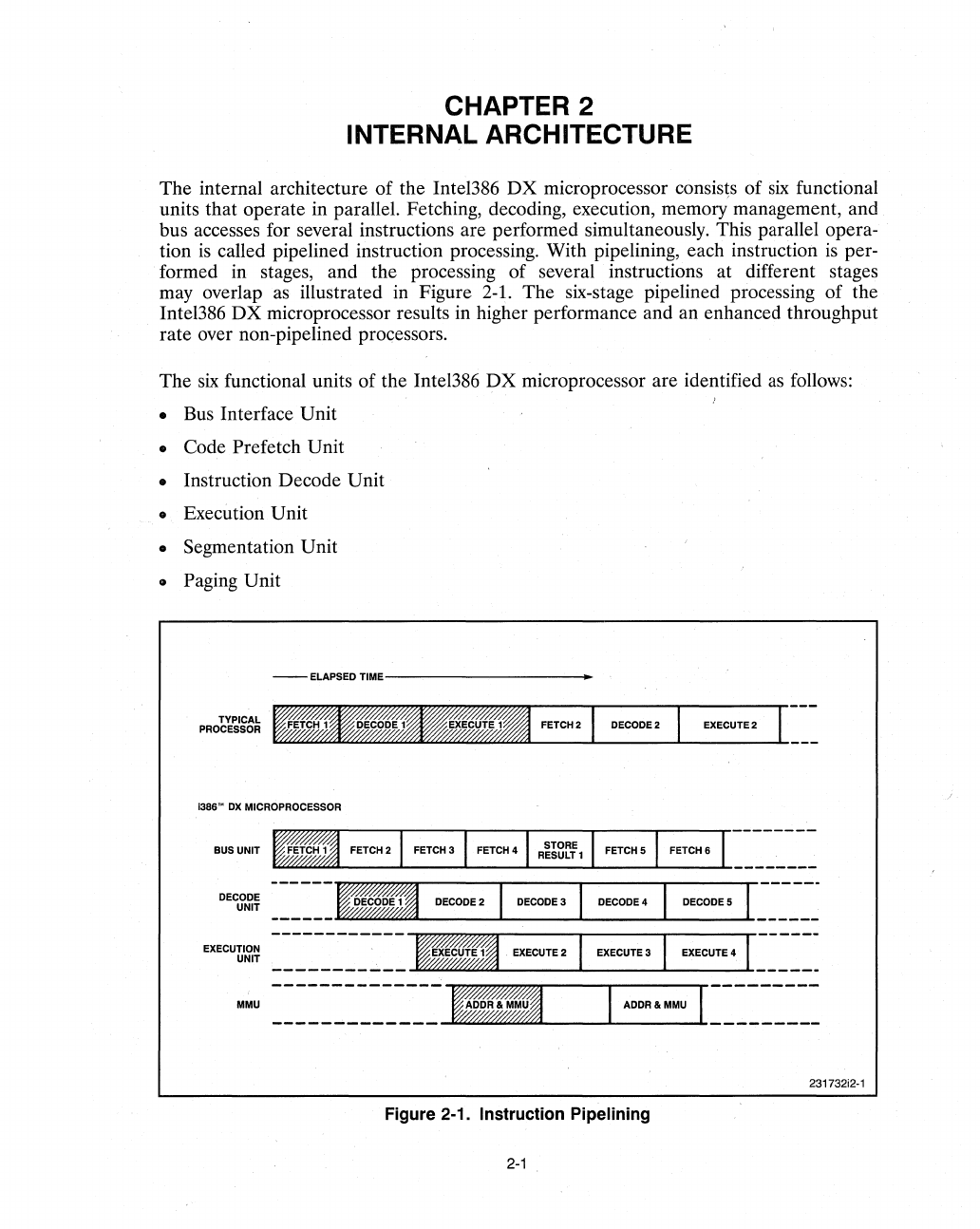

The internal architecture of the Intel386 DX microprocessor

consis~s

of

six

functional

units that operate in parallel. Fetching, decoding, execution, memory management, and

bus accesses for several instructions are performed simultaneously. This parallel opera-

tion

is

called pipelined instruction processing. With pipelining, each instruction

is

per-

formed in stages, and the processing of several instructions at different stages

may overlap

as

illustrated in Figure

2-1.

The six-stage pipelined processing of the

Intel386 DX microprocessor results in higher performance and an enhanced throughput

rate over non-pipe lined proGessors.

The

six

functional units of the Intel386

DX

microprocessor are identified

as

follows:

• Bus Interface Unit

•

Code Prefetch Unit

•

Instruction Decode Unit

•

Execution Unit

•

Segmentation Unit

• Paging Unit

TYPICAL

PROCESSDR

--ELAPSEDTIME---------

___

1386~

DX

MICROPROCESSOR

BUS

UNIT

DECODE

UNIT

EXECUTION

UNIT

MMU

~~~-~~~~~~==~""

..

:"'E."XE:~C..,U"'T:E:l:~~EX~E~C-U_T~E~2~~~-E_X-E_C~U-T_-E_3~:~~EX~E~C-U_T~E~4:1

...

~~~==~

~~~======~~-~~__"'

..

"'A"'DD"'R~&"'M"'M"'U=_

__

......J"_AD_D_R_&_M_MU____LI

~=======~

231732i2-1

Figure 2-1. Instruction Pipelining

2-1