MUL TIBUS I AND Intel386

OX

MICROPROCESSOR

r--;-

(FROM

SLAVE

INTERRUPT CONTROLLER)

8259A

0,

1.IN~TA~":CA~Sj2111--'4A2_

_

74530

CASVALlD(l)

i:

iT

74AlS580

MASTER~~~~I-~

__

""'~~

J,

OF

t-----t»-+-J"¢l~~~

(74500

L-1

___

~Aa~IA9~Al~0L-_~~

__

-L

__

r:::::::::::~sre

,/

~...

A20-Ao

'~-.--~---~

~

VMt

Of"

INTA

MCE

,...-t'-----t

.-----<~I

SYSB/R£SI!

1<

AENr--

82289

BUS

ARBITER

CENL

.....

------<JH-+-'="'"'--i-"4>-bo-t>>-+-lcMOLY

_

......

vcc':....r:

~~NL

AEN

I

MBIO'"

L----iALE

1---'----"..)

LOCALMB

~

"".

:::.:.::..-----

.....

~IM/Ill

BUS

-

CONTROLLER

WAIT·STATE

82288

-

GENERATOR

BUS

_

READY

I ....

________

~=CO::N=TR=OL:LE:R~.J

AffDYENI

..

ARCY

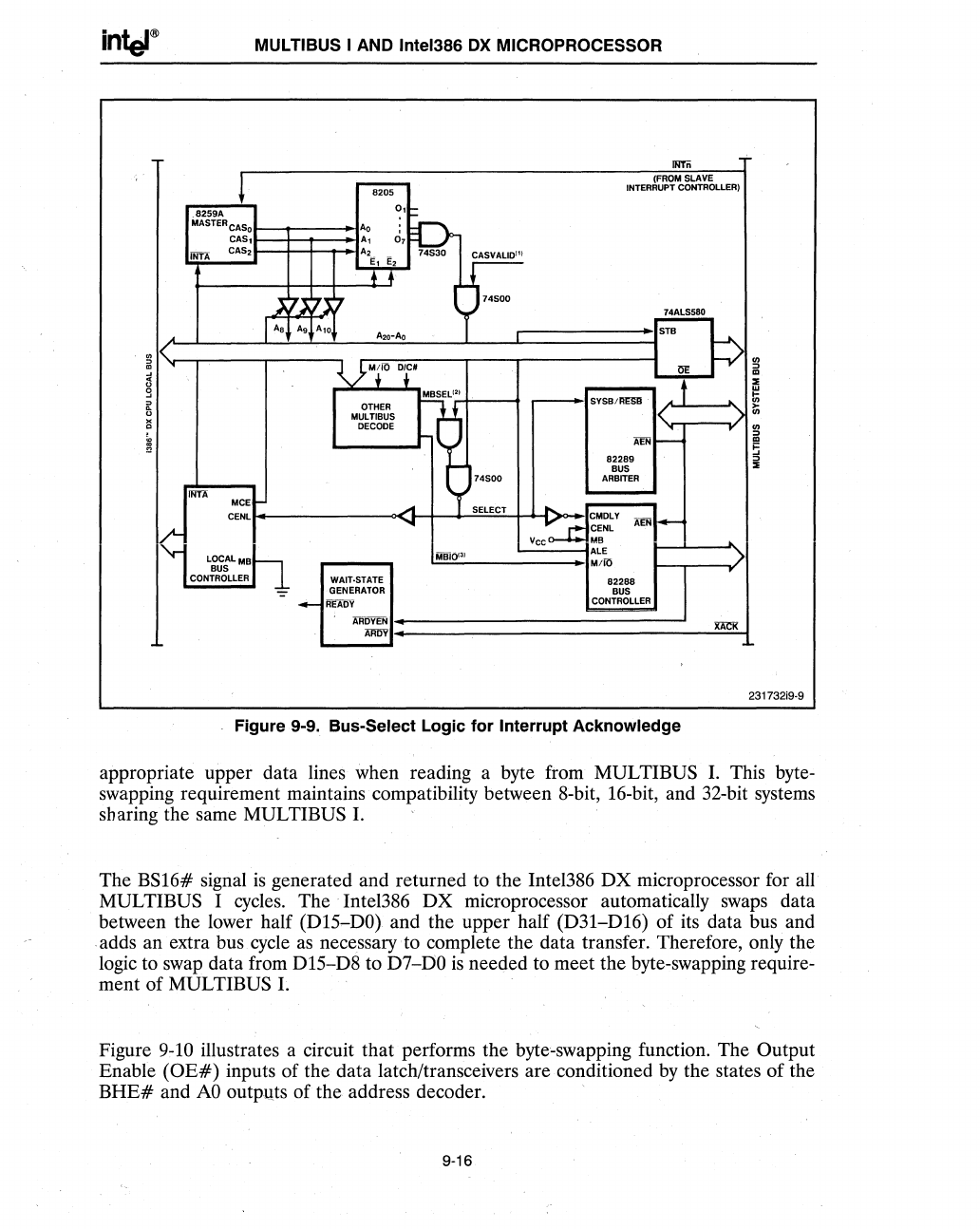

Figure 9-9. Bus-Select Logic for Interrupt Acknowledge

231732i9·9

appropriate upper data lines when reading a byte from MULTIBUS

1.

This byte-

swapping requirement maintains compatibility between 8-bit, I6-bit, and 32-bit systems

sb

aring the same MUL TIBUS

1.

The

BSI6#

signal

is

generated and returned to the Intel386

DX

microprocessor for all

MULTIBUS I cycles. The Intel386

DX

microprocessor automatically swaps data

between the lower half

(DIS-DO) and the upper half

(D3I-DI6)

of its data bus and

adds an extra bus cycle

as

necessary

to

complete the data transfer. Therefore, only the

logic to swap data from

DIS-D8

to D7-DO

is

needed to meet the byte-swapping require-

ment of MUL TIBUS

1.

Figure

9-10

illustrates a circuit that performs the byte-swapping function. The Output

Enable

(OE#)

inputs of the data latch/transceivers are conditioned

by

the states of the

BHE#

and

AO

outputs of the address decoder.

9-16